# **CADSTAR Express**

Do-it-Yourself Training Guide

# Express Do-It-Yourself Guide With Projects for Training Purposes

## Welcome!

Thank you for acquiring CADSTAR Express. This free version provides a number of features used in the full CADSTAR version, only limited by the number of components (max 50) and pins (max 300).

Electronic hobbyists, Students and Evaluators use CADSTAR Express for designing Schematics and Printed Circuit Boards (PCB). This guide will assist you in detail on how to make use of CADSTAR's features to design your next project.

- We will start by showing you a hand drawn electronic circuit and transforming it into a professional schematic design.

- We will guide you through the process of creating an error-free transfer of data to a PCB board design, and then move to component placement and wire routing.

- You will then move to the CAM output process where you will generate the necessary artwork, reports and files needed to get your PCB built by your preferred fabrication vendor.

- We will guide you through the process of creating schematic symbols, component and parts for future CADSTAR libraries.

Upon completion of this guide, you will be ready to move into higher variations of CADSTAR, offering features and constraints for High Speed signal applications and simulation as well as 3D Electro-Mechanical collaboration.

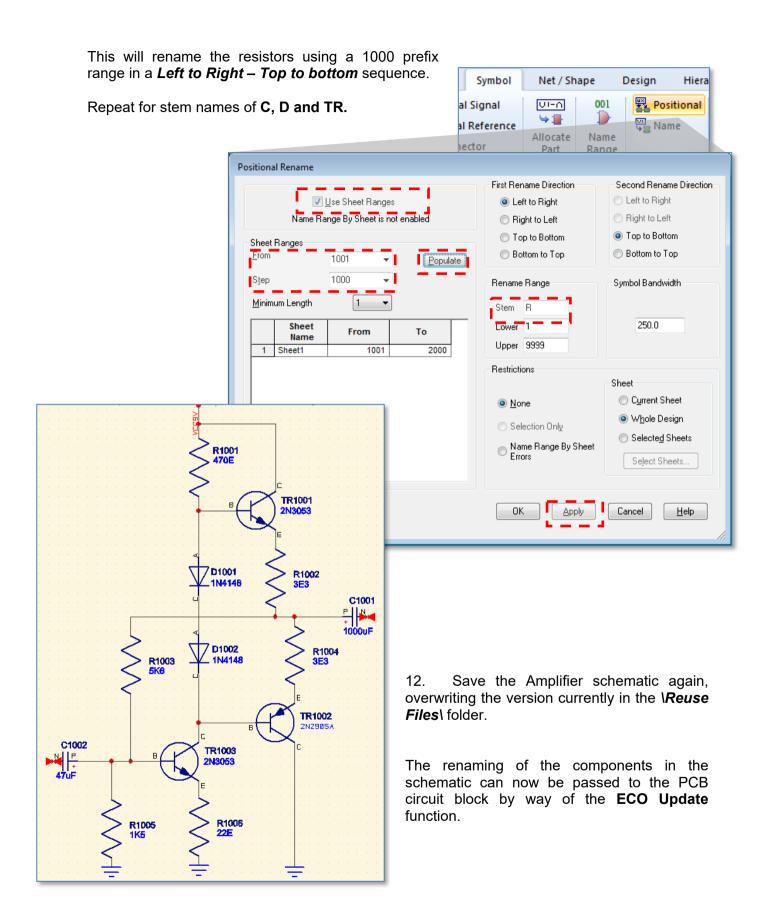

To provide you with additional "how to" information, click on the camera icons for demonstration videos. (internet connection required)

The videos are for demonstration purposes only. They are not created to match the exact instructions in the task steps. Please follow the specific steps in the tasks.

When CADSTAR Express is executed this PDF Document will appear for your convenience. If you have not installed CADSTAR Express, simply double click on the executable for set-up and follow the instructions.

As you work through the tasks in this guide, you will be instructed to save files with suggested file names. If you do not finish a task and simply wish to move on to the next task, back-up files are supplied for your convenience. Files with the "\_CS.\*" suffix can be opened and then saved using the *File* → Save as function to overwrite the file you are working on.

Enjoy!

The information in this document is correct at the time of publication and is subject to changes without prior notice. This document belongs to Zuken. No part of this document shall be copied without official written approval. CADSTAR is registered trademark of ZUKEN.

This document is given free of charge and is not for resale.

## **Contents**

| Welcome!                                               | 1   |

|--------------------------------------------------------|-----|

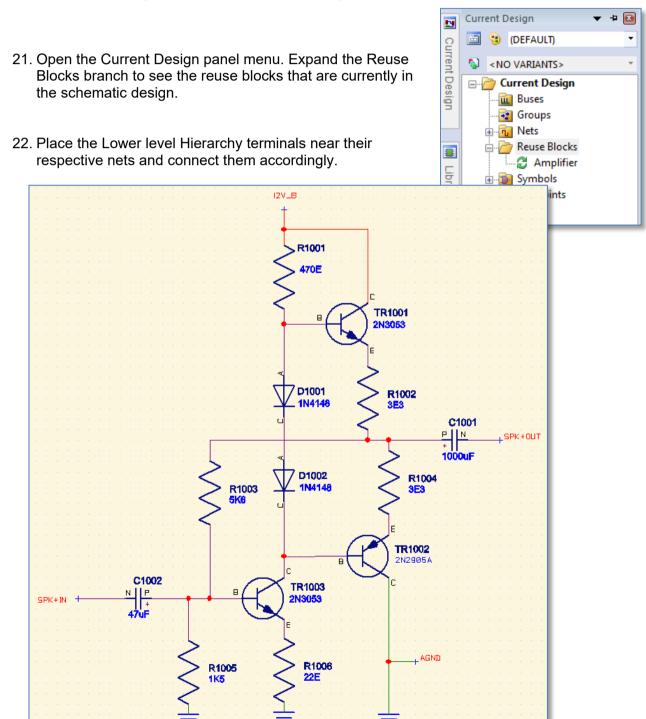

| Introduction to CADSTAR                                | 3   |

| Getting Started                                        | 4   |

| The Basic Design Flow                                  |     |

| The User Interface                                     |     |

| Strokes in CADSTAR and the Place & Route Editor        | 6   |

| Chapter 1 – Design A                                   | 7   |

| Step 1 - Schematic for Design A                        |     |

| Step 2 - PCB Placement for Design A                    | 27  |

| Step 3 - PCB Routing for Design A                      | 38  |

| Step 4 - Manufacturing data for Design A               | 42  |

| Step 5 – Saving your Design for future Reuse           | 47  |

| Add the Power of 3D to your Design                     | 53  |

| Chapter 2 – Design B                                   | 54  |

| Step 1 - Schematic for Design B                        |     |

| Step 2 - PCB Placement for Design B                    |     |

| Step 3 - PCB Routing for Design B                      |     |

| Step 4 - Manufacturing Data for Design B               | 77  |

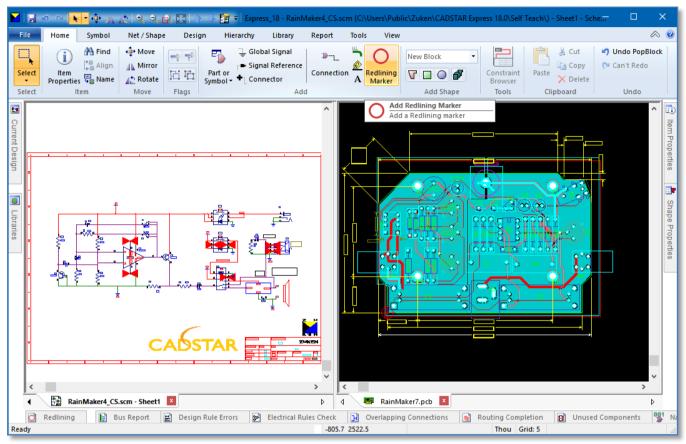

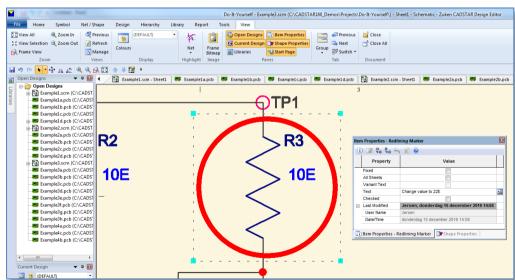

| Reviewing your Designs with Redlining Markers          | 78  |

| Chapter 3 - Library                                    | 79  |

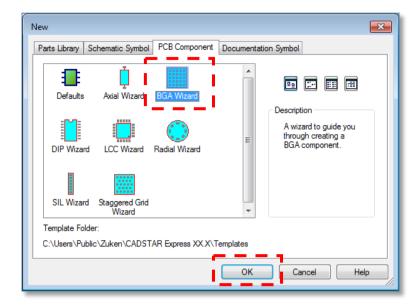

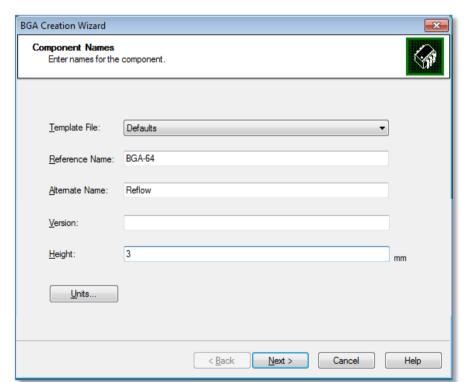

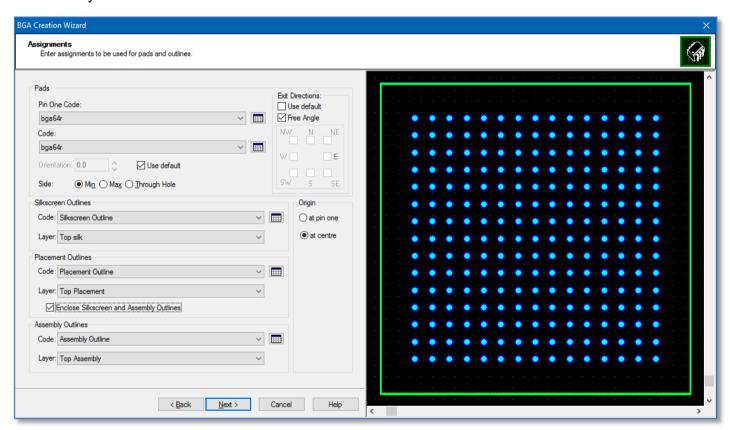

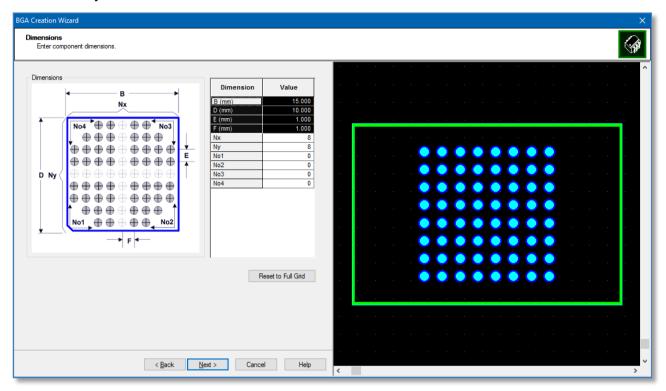

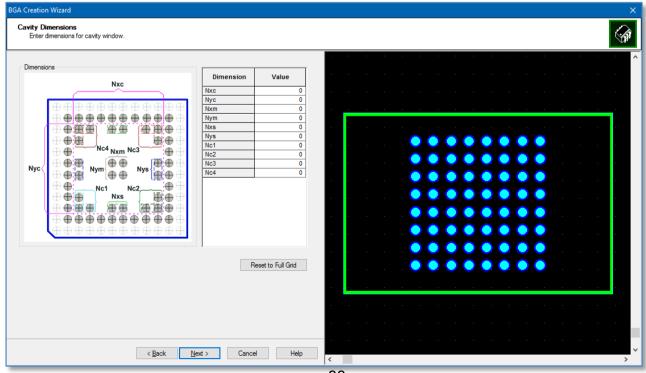

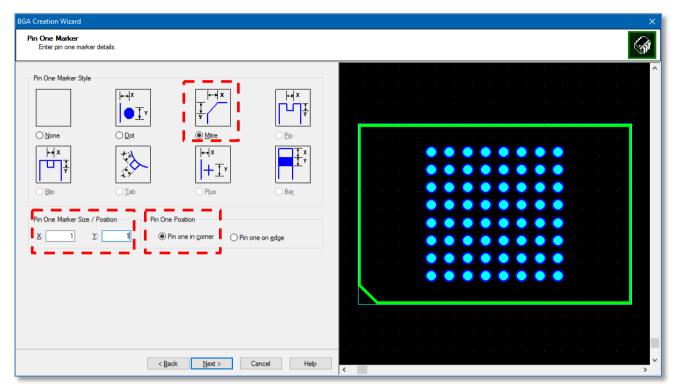

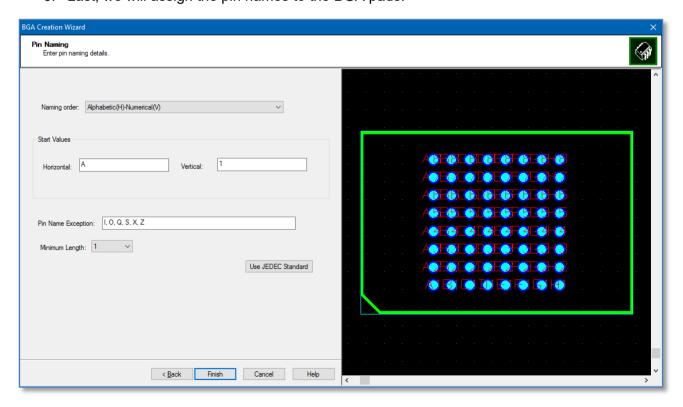

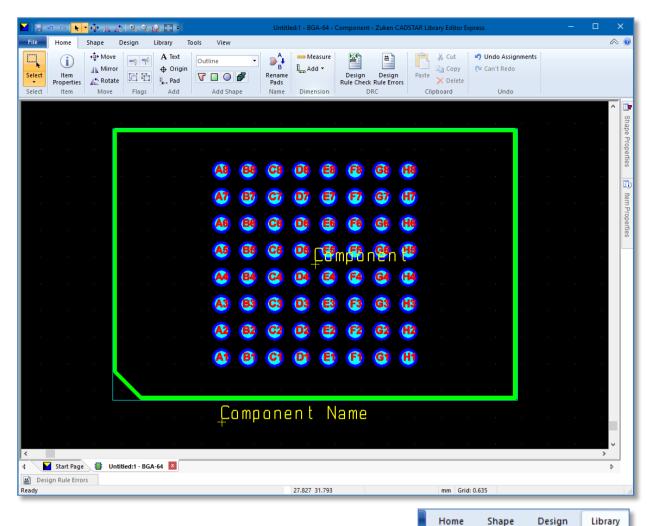

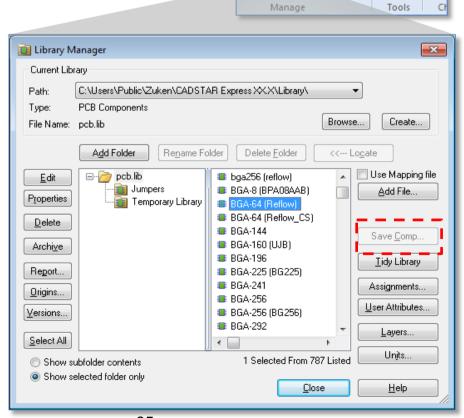

| Step 1 - PCB Component / BGA Wizard                    |     |

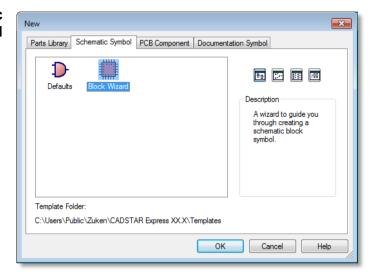

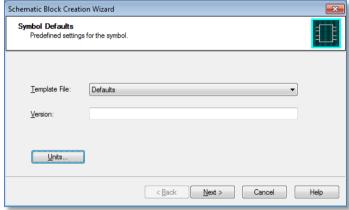

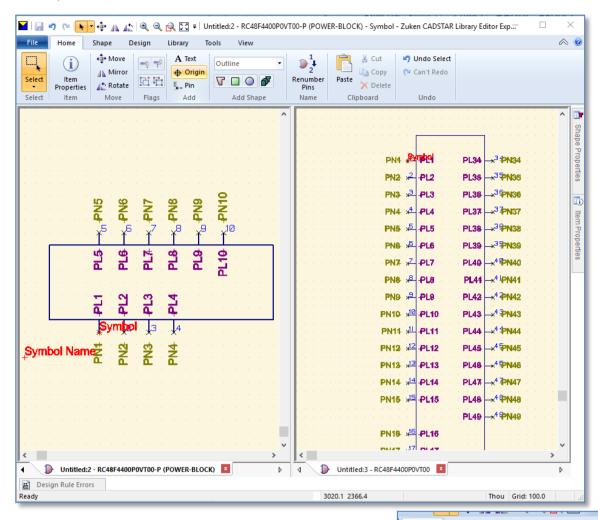

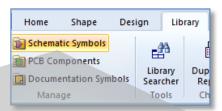

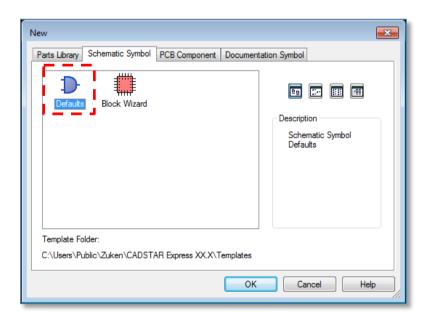

| Step 2 - Schematic Symbol / Block Wizard               |     |

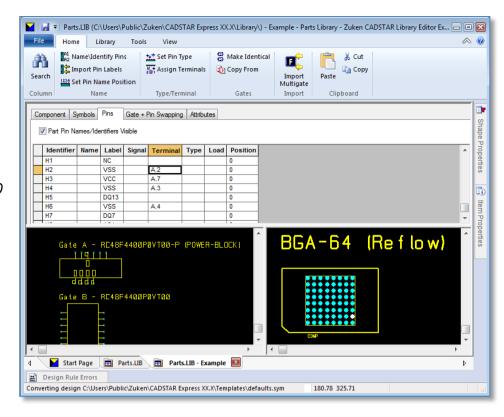

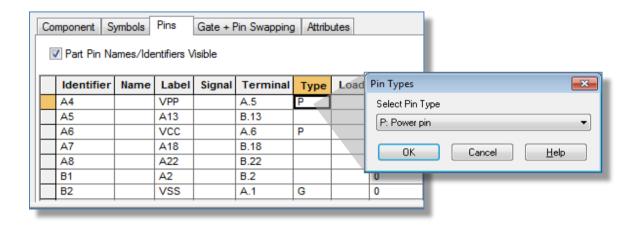

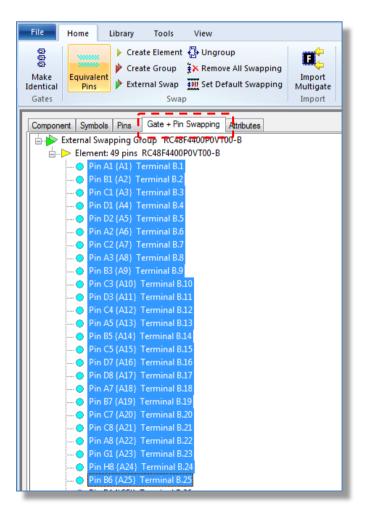

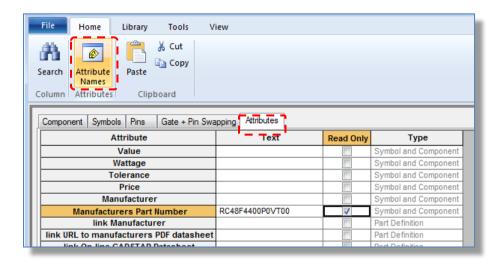

| Step 3 - Parts Library Editor                          |     |

| CADSTAR FPGA                                           | 101 |

| Chapter 4 – Design C (Standalone Place & Route Editor) | 102 |

| Step 1 - Schematic for Design C                        |     |

| Step 2 – Placement for Design C                        |     |

| Step 3 - PCB Routing for Design C                      |     |

| Step 4 - Manufacturing Data for Design C               | 123 |

| Chapter 5 - Design D (Single Sided Board Design)       | 124 |

| Step 1 - Design D                                      |     |

| Step 2 - PCB Placement for Design D                    |     |

| Step 3 - PCB Routing for Design D                      |     |

| Step 4 - Manufacturing Data for Design D               |     |

| Conclusion                                             | 131 |

|                                                        |     |

Please Note: This do-it-yourself guide has been revised using a Windows 10 environment. The software has been installed on the author's computer using the default locations and selections per the CADSTAR Express SETUP program. CADSTAR Express is also supported using Windows 8.

Last updated: 30 June 2020

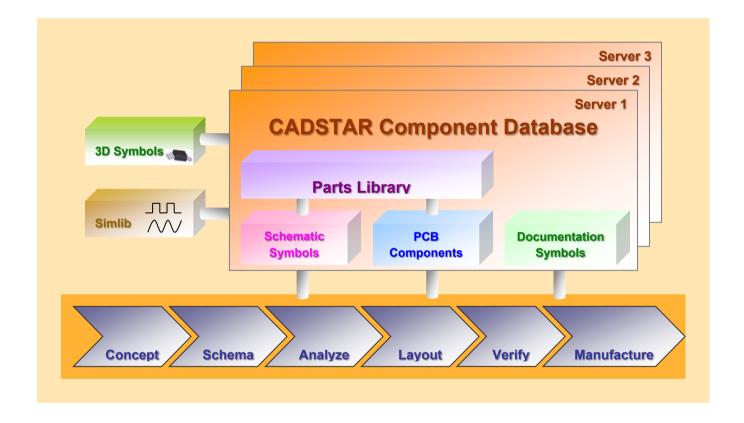

## Introduction to CADSTAR

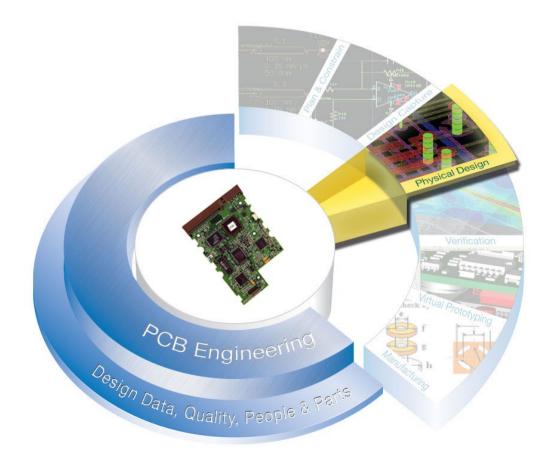

CADSTAR is an EDA design tool allowing you to draw schematic designs and transfer them to the PCB layout environment. After an error-free transfer, CADSTAR helps to place the components into the board outline.

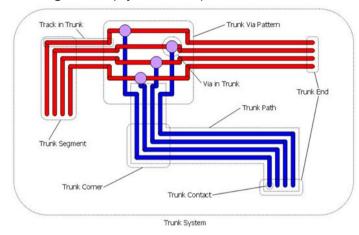

Placement and Routing is an integral part of a PCB design process. CADSTAR offers much flexibility in this area by providing both Push-aside Placement and Routing tools (manual, semi-automatic and fully automatic) within the Embedded Place & Route Editor or the advanced standalone Place & Route Editor. The Embedded Place & Route Editor has been developed in general for basic PCB design or users who don't use a PCB design tool regularly, and the standalone Place & Route Editor is for the more advanced users who require more powerful functions. For really advanced users (industry users) high-speed design features (such as lengthening, delay, impedance, cross-talk, overshoot, reflection etc.) can also be provided in a full standard package or as an optional add-on. The additional add-ons that are available to you, include **BoardModeler Lite** which is a *unique* 3D verification tool for PCB design that provides a completely new concept of PCB Design in a 3D environment or the CADSTAR Variant Manager which enables you to generate variants of a 'master' design (included B.O.Ms and assembly drawings) without having to maintain separate files for each variant.

The completion of the PCB design is followed by the generation of manufacturing output data for PCB fabrication.

## **Getting Started**

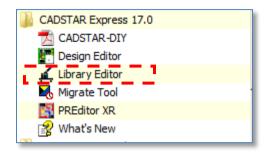

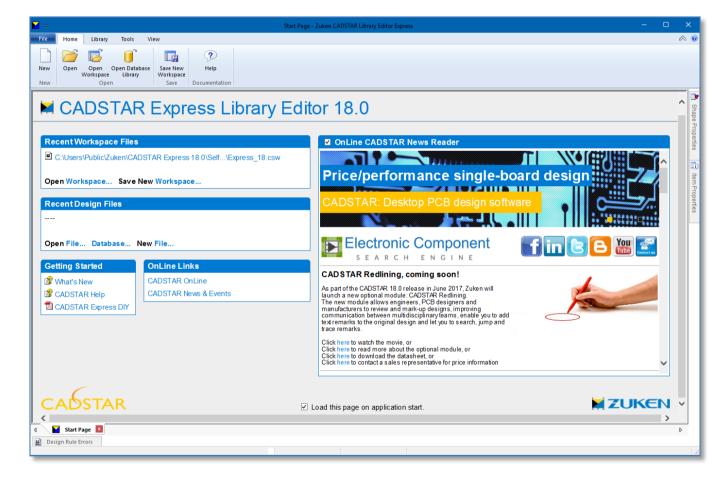

By now you have probably installed CADSTAR on your PC and are anxious to get started. Start by clicking the **Design Editor** Icon in your **Start >All Programs >CADSTAR Express XX.X** menu. When CADSTAR is started you will see the **Start page** as shown below.

#### It allows you to;

- Access recently opened Workspace Files.

- Access recently opened Designs.

- Access Help and PDF files.

- Read up on the latest in CADSTAR News from the World of Zuken.

- Access some On-line Links such as the CADSTAR Web pages.

CADSTAR is a Multi-Document Design Environment. Soon you will have schematic designs and PCB designs all open in the same *Design Editor* environment.

## The Basic Design Flow

#### Library

Usually you need to start off with a library to ensure that all the parts (schematic symbols & PCB footprints) required for your design are available to you. However, to complete the exercises in this guide, all parts have been provided. When you are ready to create new parts in the CADSTAR library, please study chapter 3.

Note: the library provided with CADSTAR Express contains all the parts required for the PCB designs described in this 'Do-It-Yourself" guide as well as some examples from the on-line CADSTAR Libraries. (Accessing the CADSTAR On-line libraries requires a higher variation of CADSTAR and an active maintenance contract).

#### **Schematic**

It is always advisable to start with a schematic design before moving onto the PCB design, although CADSTAR does support reverse engineering with full back annotation capabilities.

## PCB

After the successful transfer from schematic, components will be placed within the (Placement) board outline and respective placement areas.

## **PCB** (Routing)

After placing all the components, we can start routing the critical nets manually and/or through automatic routing.

# Manufactu-

The final stage of any PCB design. No matter what your manufacturer requires, ring Output CADSTAR can deliver; extended Gerber (RS274X), extended N.C. Drill (Excellon), Placement data, Bill of Materials, IPC356-D test data, DXF and ODB++

## The User Interface

CADSTAR is very easy to use! The User Interface is very consistent in operations whether you are editing a Schematic or a PCB Design.

## CADSTAR Supports;

- Ribbon style Tool bars can be dragged and docked as needed

- Tool bar Icons that can be allocated as the user wishes

- Customizable Tool bars and Menus are supported for adding user defined reports and Macros

- Tabbed Document Window support Most often seen in more modern version of Windows 10 and MS Office ®

- "Strokes" command macros that perform the most common functions for panning and zooming

- Omnidirectional panning by depressing the middle mouse button or <M.M.B.>

- Themes to alter the appearance of CADSTAR when working in a more modern operating

- Active HTML reports Active HTML reports can be placed anywhere just like any other dockable window in CADSTAR. The reports you currently have open will appear as tabs in the Active Report window

## Strokes in CADSTAR and the Place & Route Editor

If you are not familiar with Stroke commands, you can use them for;

Indicating operations you wish the application to perform by dragging the right mouse button in the shape of one of the 'gestures' in the table below.

#### To make the gesture:

- Use the mouse to position the cursor in the design window

- Click the Right Mouse Button or <R.M.B.> and Hold while moving the mouse so that the cursor follows the path of the gesture. The application will provide feedback by drawing a white line showing the path of the cursor

- Release the right mouse button

**Note:** The shape of the path followed by the cursor is important. The direction which the cursor takes along the path is also important, since it is often true that each of the two different directions is associated with a different operation.

| Gesture | Icon     | Operation                                                                                            | Gesture   | Icon     | Operation                                                                                           |

|---------|----------|------------------------------------------------------------------------------------------------------|-----------|----------|-----------------------------------------------------------------------------------------------------|

| 1       |          | Pan up                                                                                               | <b>——</b> | 1        | Pan left                                                                                            |

|         | <b>T</b> | Pan down                                                                                             | <b>→</b>  | <b>D</b> | Pan right                                                                                           |

|         | €.       | Zoom in                                                                                              | /         | Q        | Zoom out                                                                                            |

|         |          | View all<br>(Display all of the<br>drawing/design or<br>component/symbol)                            |           | Q        | Zoom to selected<br>area<br>(the minimum box<br>which contains both<br>the start and end<br>points) |

|         | <b>P</b> | Redisplay the current<br>view, repairing any<br>damage to the<br>objects displayed                   | Z         | Q        | Zoom to selected<br>area<br>[see above]                                                             |

|         | Q        | Previous View Revert to the view as it was before the last view-changing command such as pan or zoom |           |          |                                                                                                     |

## Chapter 1 - Design A

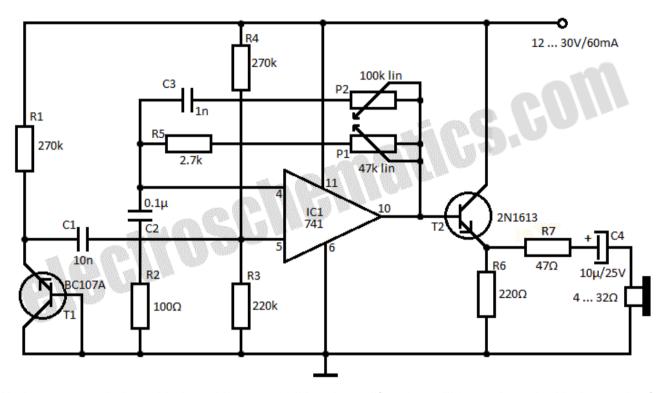

## Introduction to the Amplifier circuit

Transistor Audio Amp (50 mW)

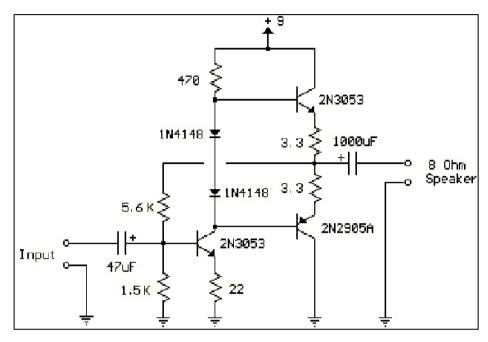

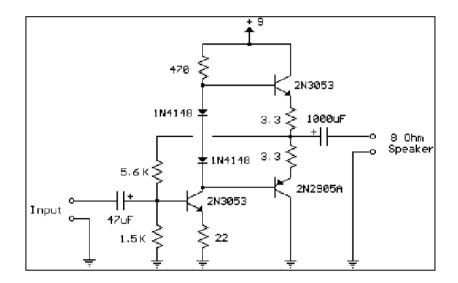

## Information on Design A - Transistor Audio Amplifier

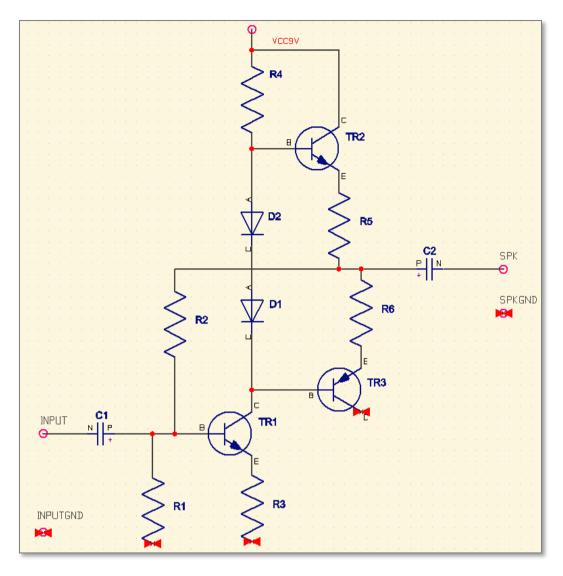

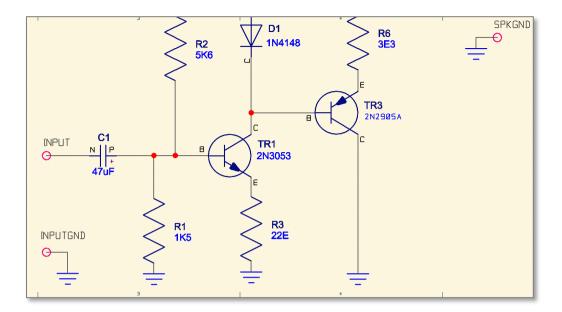

Here is a little audio amplifier, similar to what you might find in a small transistor radio. The input stage is biased so that the supply voltage is divided equally across the two complimenting output transistors, which are slightly biased in conduction by the diodes between the bases.

A 3.3 Ohm resistor is used in series with the emitters of the output transistors to stabilize the bias current so it doesn't change much with temperature or with different transistors and diodes. As the bias current increases, the voltage between the emitter and base decreases, thus reducing the conduction.

Input impedance is about 500 Ohm and voltage gain is about 5 with an 8 Ohm speaker attached. The voltage swing on the speaker is about 2V without distorting and power output is in the 50mW range. A higher supply voltage and the addition of heat sinks to the output transistors would provide more power. The circuit draws about 30mA from a 9-12V supply.

## Step 1 - Schematic for Design A

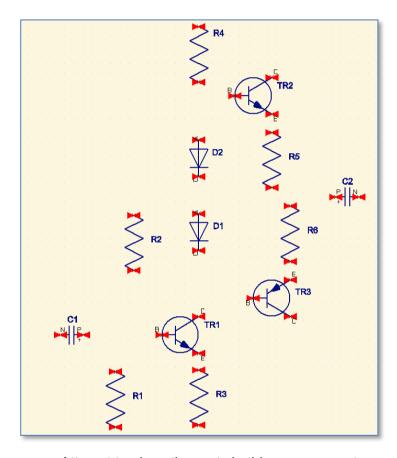

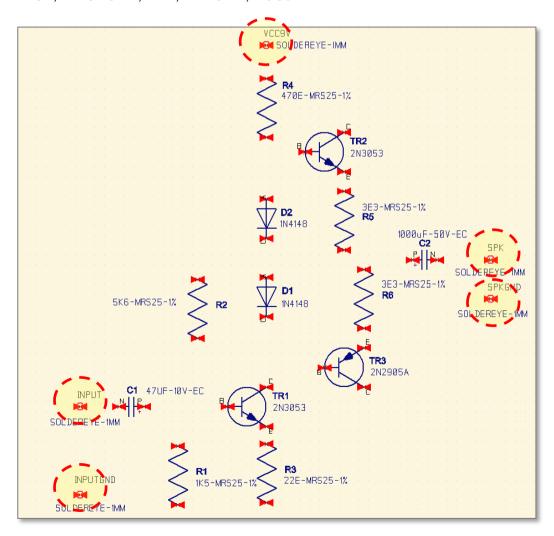

Start by reviewing the hand drawn schematic shown previously - the design of the audio amplifier. You will then have to gather the components being used in the circuit

From the hand-drawn schematic, you will find twelve (12) parts in the Library. They are;

Qty. per Part

| , , |                                   |                                        |

|-----|-----------------------------------|----------------------------------------|

| 2   | 2N3053 NPN Transistor             | 1 470 Ohm Resistor (470E-MRS25-1%)     |

| 1   | 2N2905A PNP Transistor            | 1 1.5 kOhm Resistor (1K5-MRS25-1%)     |

| 2   | 1N4148 Diode                      | 1 5.6 kOhm Resistor (5k6-MRS25-1%)     |

| 2   | 3.3 Ohm Resistor (3E3-MRS25-1%)   | 1 47uF/10V Elec. Cap (47uF-10V-EC)     |

| 1   | 22 Ohm Resistor (22E-MRS25-1%) -  | 1 1000uF/50V Elec. Cap (1000uF-50V-EC) |

| 5   | SOLDEREYE 1MM (for Input, Speaker | and 9V supply)                         |

You can use a 9V battery for this power supply.

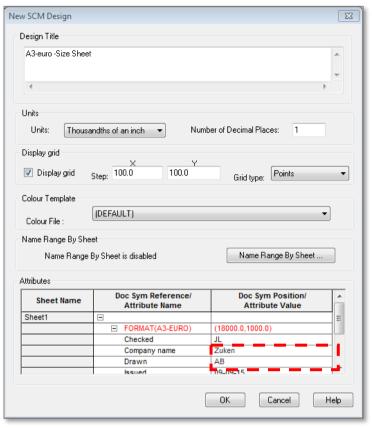

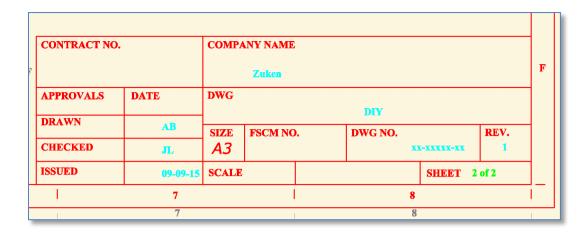

Click the New icon on the [Home] tab or select [File] tab→New [Schematic Design] and choose one of the templates such as Form A3-euro.

Once you select a template you are prompted with parameters to enter information using the *Attributes* that have been created for you.

2. If you like, enter your company name and personal name in the attribute fields below.

These will appear in the Title block of the Schematic format symbol. Later you can easily customize your own attributes and format sheets.

**TIP:** If you don't like to work with a black background, you can also select a different background colour scheme from the toolbar.

3. Click [OK]

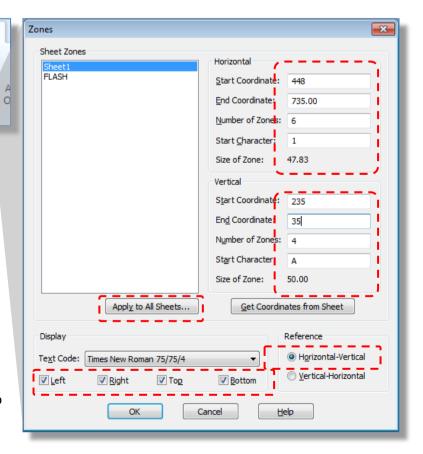

**Note:** If you are creating larger schematics using many sheets, you may choose to declare reference designator name ranges **By Sheet**. Clicking the button shown above will display the dialog shown below. For this design we will only need one sheet.

You have just started a new untitled, schematic design. Select the [File]→Save as...] Name it DesignA1.scm

You can now start to add the parts and symbols required using the **Libraries** auto-hide panel on the left of the application window. For a demonstration click the camera Icon.

**Note:** The Auto-hide panels for Libraries, Designs, Shape Properties, etc., can be automatically hidden if you wish. Simply click the **Auto Hide** Icon shown below. When you move your cursor off of the workspace panel it will automatically slide to a hidden position. To show the panel again, drag your cursor back to the desired Workspace panel tabs on the left-side of the application window. When it appears click the **Auto Hide** push pin icon to hold it open.

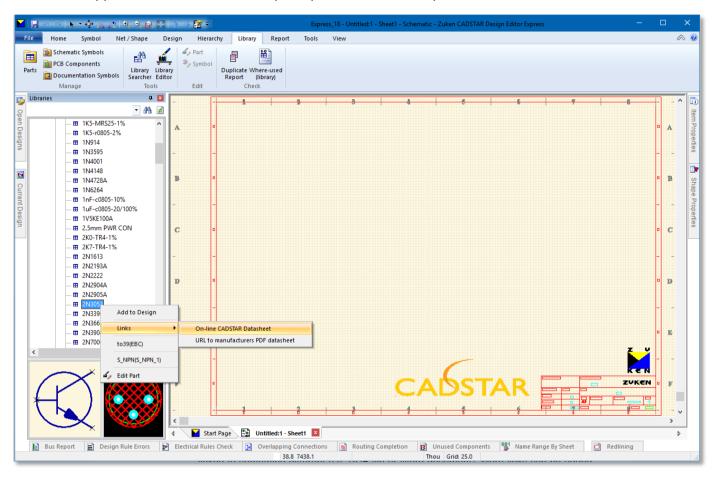

**Tip**: When adding the part/symbols into the design (like 2N3053), you can select the symbol and *click* on the right-hand mouse button <**R.M.B.**> to see a *Link: On-line CADSTAR Datasheet*. The link is a hyperlink to a URL on the internet (or intranet), but can also be linked to something different (i.e. PDF file or Word document). More links can be added to parts in the CADSTAR Parts Library Editor. Be aware that some links might be out of date as the part may be obsolete.

Add Parts and Symbols

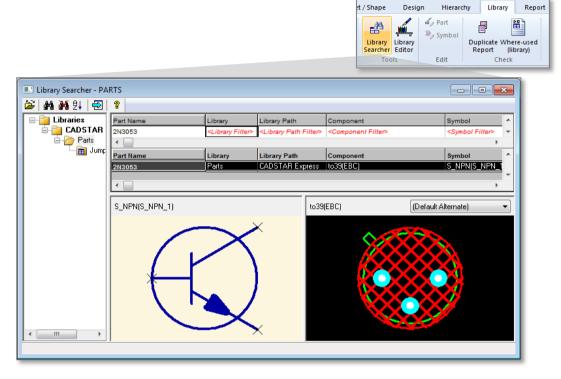

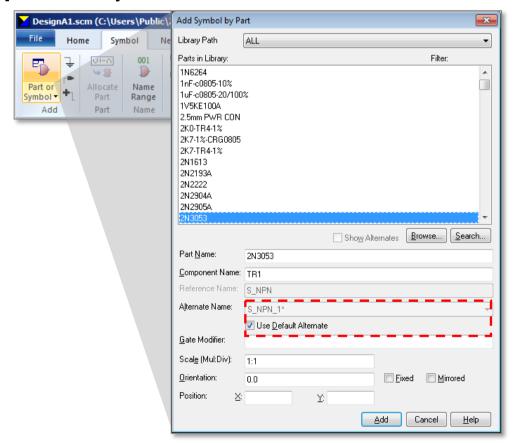

For advanced library searching and filtering try one of the additional following methods. Both allow you to specify which alternate symbol to use if available.

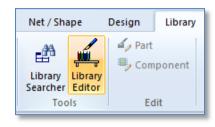

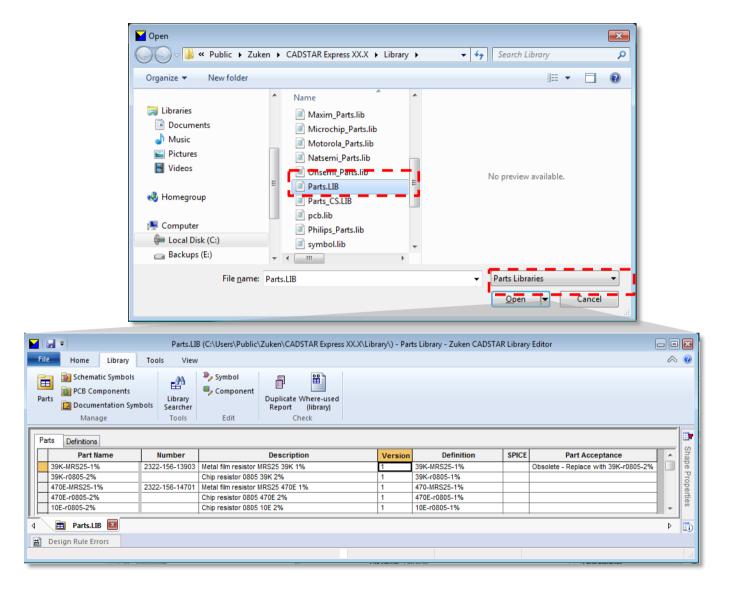

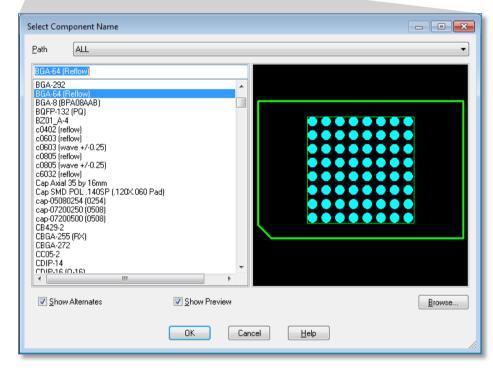

• From [Library] tab click the Library Searcher function. Select the Parts.lib (or any of the other Parts Libraries you want to search).

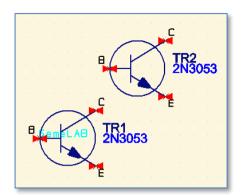

• [Symbol] tab → Part or Symbol

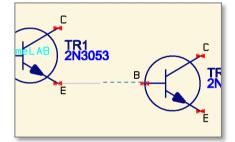

4. Place two 2N3053 transistors onto the schematic by clicking the Add to Design option or by dragging the transistor from the Libraries panel, i.e. highlight 2N3053 for a TO-92 package, click and hold the left-hand mouse button down, without releasing it and drag it on to the sheet.

Don't be concerned about the red bow-tie markers on the pins. They highlight unconnected pins (the markers will disappear once you connect the pins).

While dragging, you can use the right-hand mouse button for mirror and/or rotation for the placement of a symbol, use the 'm' or 'r' hotkeys, or use a programmable function key like <F3> to rotate.

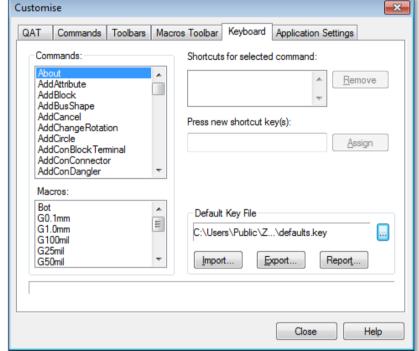

**Tip:** You can setup the function keys by selecting the [**File**] tab and the Customize button at the bottom, right of the menu.

**Tip:** For more information on hot key commands type '?<enter>' (this will appear on the command line at the lower left corner of the application).

5. Do the same for the other 11 parts (you can either select the through-hole or SMD components):

| Qty. | Part                                 | Ref des |

|------|--------------------------------------|---------|

| 1    | 2N2905A PNP Transistor               | TR3     |

| 1    | 1.5 kOhm Resistor (1K5-MRS25-1%)     | R1      |

| 2    | 1N4148 Diode                         | D1, D2  |

| 1    | 5.6 kOhm Resistor (5k6-MRS25-1%)     | R2      |

| 1    | 22 Ohm Resistor (22E-MRS25-1%)2      | R3      |

| 1    | 470 Ohm Resistor (470E-MRS25-1%)     | R4      |

| 2    | 3.3 Ohm Resistor (3E3-MRS25-1%)      | R5, R6  |

| 1    | 47uF/10V Elec. Cap (47uF-10V-EC)     | C1      |

| 1    | 1000uF/50V Elec. Cap (1000uF-50V-EC) | C2      |

Attempt to place the parts in this arrangement.

- 6. You can move more than one symbol at a time. Hold down the <Ctrl> button on the keyboard and make your selections and then *Click and Drag* them.

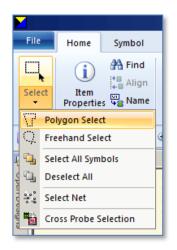

- 7. Try using the **Polygon Select** and **Freehand Select** functions to select everything within an area. Select the **Home** tab and click **Select** icon to access various selection tools. Select **Polygon Select** and draw a polygon/fence around the items you want to select. When you are ready to select them double-click the left mouse button to accept the polygon or if using the freehand selection mode, just release the left mouse button and then *Click* and *Drag* them.

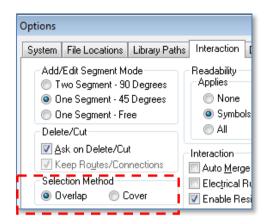

An additional selection method is available in the [File] tab-Options-[Interaction]. Here you can choose between Overlap and Cover selection methods.

This gives more control over how items are selected during Frame Select, Polygon Select and Freehand Select.

- Use **Cover** to only select items completely covered by the selection shape.

- Use Overlap to select items partially covered by the selection shape.

A different cursor is displayed to show which selection method is in use. The selection method can be toggled by right clicking whilst drawing a selection shape. I.e. Holding down the **L**eft **M**ouse **B**utton and clicking the **R**ight **M**ouse **B**utton.

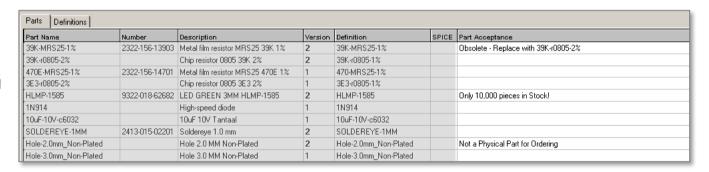

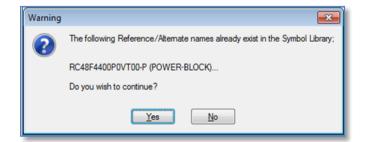

**Note:** When adding parts you be may prompted with a Warning!. This can be controlled by using a special attribute value to control "**Part Acceptance**".

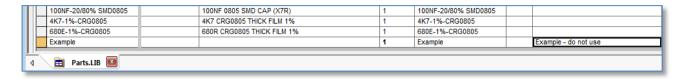

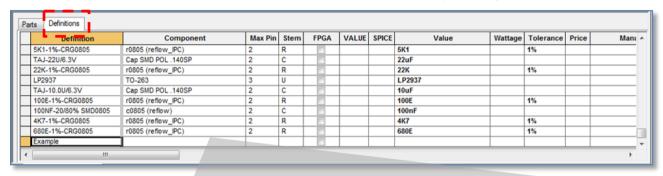

In the Parts Library image shown above, the column labelled "Part Acceptance" can hold a unique text reference to communicate a Part's Life cycle or inventory control measure to the user. This can be defined by the Librarian.

Warning!

When a part containing a Part Acceptance value is added to a schematic design, the following warning dialog will be displayed.

Accepting this part will also store its value in the

design for later reflection in parts List

and various other report outputs.

The property will be reflected in the Item Properties dialog.

| Part Details     |                                                              |

|------------------|--------------------------------------------------------------|

| Nam <u>e</u> :   | 39K-MRS25-1%                                                 |

| Number:          | 2322-156-13903                                               |

| Description:     | Metal film resistor MRS25 39K 1%                             |

|                  | {Express}\Parts                                              |

| Part Acceptance: | Obsolete - Replace with 39K-r0805-2%                         |

|                  | Design Version: 1 Part Pin Names/Identifiers <u>V</u> isible |

|                  | Library Version: 1                                           |

Do you wish to continue?

<u>Y</u>es

Part '39K-MRS25-1%' :- Obsolete - Replace with 39K-r0805-2%

<u>N</u>o

×

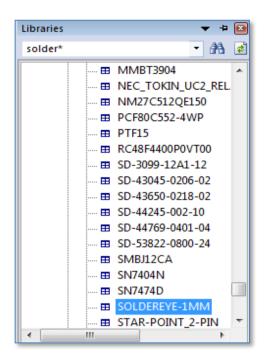

8. After all the components have been placed, perform a Library search for SOLDEREYE-1MM. You can use the wildcard and search for solder\*. You can then add these parts to represent the 8 Ohm Speaker, Input and +9V terminals (see schematic diagram on page 6). These parts will serve as the wire connections to the battery pack, signal input and speaker outputs.

These parts are created as single pin **Testpoint** components. You could also add these by using the Add Testpoint command.

Parts are assigned the next available Reference Designator per the design or the sheet. There are several ways to name or rename parts, such as with the Item Properties dialog.

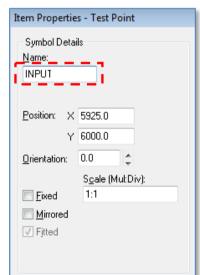

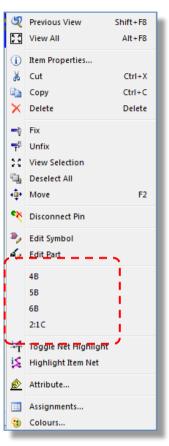

Change the Symbol Properties name for one of the SOLDEREYEs to "INPUT". To change the name, select one of the parts then click the <R.M.B.> and select Item Properties.

Enter the corresponding name per the parts placement image on the previous sheet. Click the [Close] button and select the next Solder Eye part.

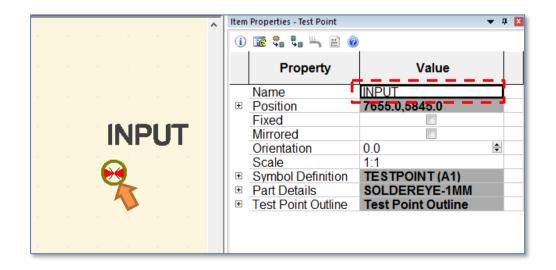

You may repeat the same technique or use the **non-modal Item properties** auto-hide panel on the right side of the application window.

10. Pass the cursor over the *Item Properties* panel button to reveal the panel dialog. Set the pin icon to leave the auto-hide panel open for as long as necessary.

With the panel open, the properties of any item selected will be represented. Many fields are editable. Functions such as Reload and Replace parts can be executed from the dialog. Other icons provide access to the standard *Item Properties* dialog and the *Attribute Editor*.

Use this option to name the SOLDEREYE parts according to the previous parts arrangement image. Simply select a part and enter its name one at a time. Since this is non-modal there is no need to close the dialog.

Place INPUT, INPUTGND, SPK, SPKGND, VCC9V as shown below.

## Adding Connectivity

Adding connections can be achieved several ways.

a. Select the **Home** [tab] and click the **Add Connection** function. Click on a pin to start the connection, and move your cursor to your destination pin to complete the connection. The **Connection** function is also located on the **[Net/Shape]** tab.

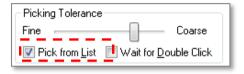

**Note:** By default, clicking on a pin will display a selection list. To disable this mode, select the **[File]** tab → **Options→[Interaction]** tab and uncheck the **Pick from List** setting. By disabling this, connections can be added in a non-modal method by double clicking on the pin.

- b. You can place the connecting terminals (pins) on top of each other, then drag them apart to see the connection. Pins that are connected will be automatically hidden.

- c. You can use the left mouse button <L.M.B.> to click (hold and drag momentarily) from the red bow ties displayed on unconnected pins and click the left mouse button over another red bow tie to finish. Corners can be added along the way by also clicking the <L.M.B.>.

CADSTAR allows you to make pin names or numbers visible/invisible (this is typically determined by the librarian) such as for 2 pin non-polarized devices. If these parts are set to be invisible the user can override them globally as follows.

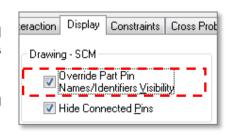

11. Select [File]tab→Options→[Display] from the ribbon and enable/disable Override Part Pin Names/identifiers Visibility.

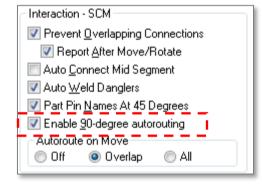

CADSTAR provides an Interactive check for flagging overlapping connections.

12. Select the [File]→Options→[Interaction].

When the **Prevent Overlapping Connections selection** is enabled, the check will alert you with the following error when you attempt to drag a connected terminal of any sort and place it on top of a connection line of a different net name.

OK

Cannot complete operation - connections overlap

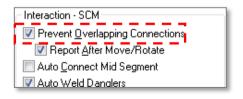

If you do not wish to run the interactive check until a more convenient time, simply disable the selection. When you are ready to perform a batch check of the design, move the cursor over the Overlapping Connection active report button to make the report panel open.

Click the **Overlapping Connection** report button as shown above. The resulting report contents are hypertext. Selecting a line item will make the error appear in the schematic window.

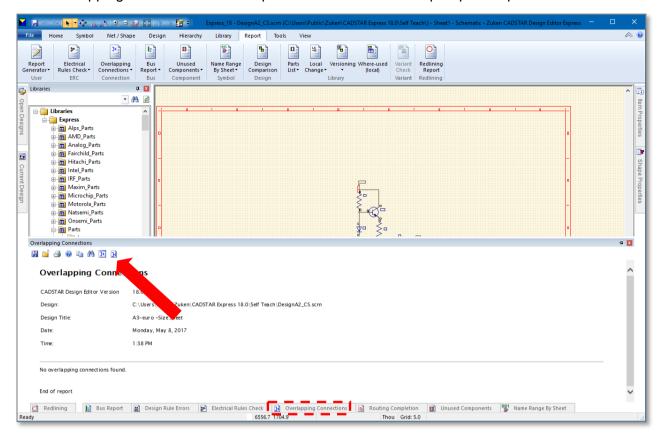

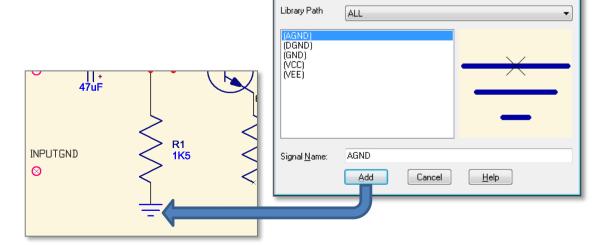

13. Add five AGND Global Signal symbols as shown in the diagram. To do so, click the **Global Signal** button located on the Symbol tab.

Select (AGND). You can connect the AGND terminal and the terminal of resistor R1 by placing the terminals onto each other as shown below.

Add Global Signal

×

14. Finish connecting all the symbols together as shown on the previous page. To connect, try each of the methods as previously described.

When you are adding a connection (Add Connection) or editing a connection (Add/Edit Segment) the route taken by the connection will automatically avoid obstacles in its path. This can be enabled/disabled in the [File]-Options-[Interaction].

When connecting, you can also use the right-hand mouse button <**R.M.B.**> to **Change Default Net Route Code**, allowing you to select a different Net-Route Code for the PCB design. (I.e. wider than signal tracks for Power & GND).

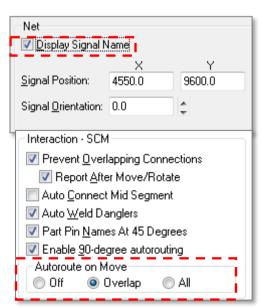

- 15. Change the net name connected to VCC9V to VCC by selecting the net 💌 and clicking the Item Properties icon.

- 16. Select the pins of the AGND symbols and click the Item Properties icon. Check the **Display Signal Name** option to display the AGND signal names.

**Note:** this is for display purposes only. If you decide to not show the signal names they would still remain AGND.

**Note:** Moving connected symbols maintains connectivity as you would expect. A connection autorouter corrects the 90 degree orthogonal patterns in real time. However this can be disabled if you wish.

If Automatic Version Increment in [File] >Options > [System] is enabled, with every future change of a symbol, component and part, the version increments automatically as it is saved to the library. You can easily check if a component in your Schematic or PCB design matches the current Library version. To check, click Reload located on the Symbols tab.

This function is also used to reset all selected parts, Label, Symbol and Part name attributes to their original locations as defined in the library by selecting a **Reset to Origin** option.

The image The image shown above is an example that shows the dialog when Parts are different than those in the Parts Library.

17. When completed, save this schematic design as **DesignA2.scm**. If you didn't complete the schematic design as described above, just open DesignA2\_CS.SCM and save it to overwrite your file.

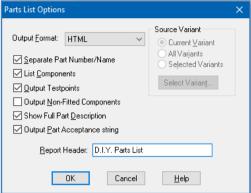

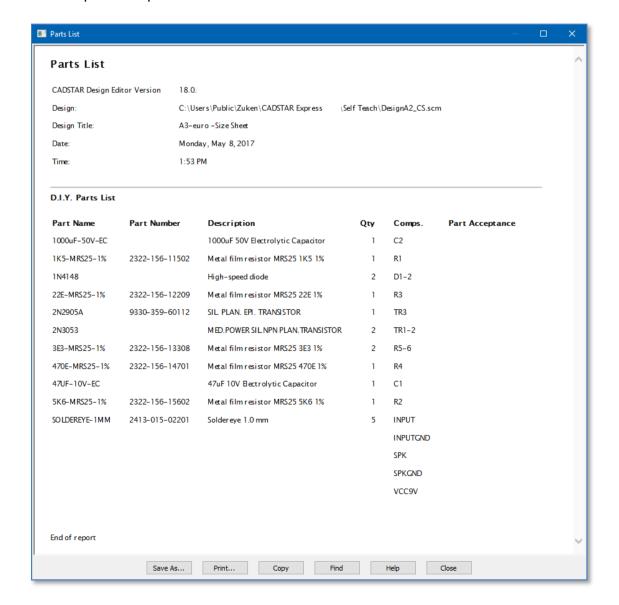

18. In today's market it is important to deliver a B.O.M. (Bill of Materials or in CADSTAR called Parts List) at an early stage.

To create a parts list, click the upper half of the **Parts List** button.

To modify the options select the lower half of the **Parts List** button.

The output shown below includes the Parts description and the Testpoint components.

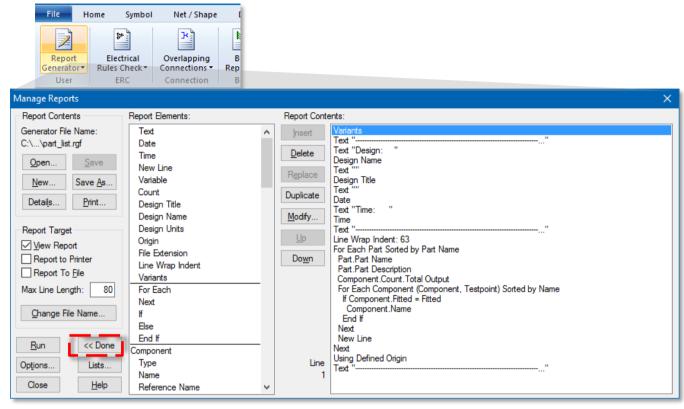

If you prefer to create a Parts List in a different format (fully customizable) click on the **Report Generator** button also located on the **Reports** tab.

In the above image the dialog is fully enlarged as a result of clicking the **[EDIT]** button. Once enlarged the button will change to **[Done]** thus serving as a toggle function.

Open the file *part\_list.rgf*, which you can find in the *Reports* directory and just click [**Run**]. You can customize the parts List output and list any attribute (wattage, voltage, tolerance, manufacturer etc.) in any particular order you choose.

For the more advanced users among you who have experience in Visual Basic or C++, you can create, for example, a user-defined B.O.M in Microsoft Office Excel, by using the OLE automation in CADSTAR.

- 19. To print your schematic design, simply click on [File]→Print and go through the Print and Page Setup. Alternatively you can print your schematic design to a PDF file, you do not need to install a PDF writer, CADSTAR has its own native PDF writer.

- **Tip:** Enable Alternative text output in the print options, making text **searchable** when printing to a file format such as **PDF**.

View File

Design:

Date:

Design Title:

Collation Results:

0 group(s) A reuse block(s)

PCB design has:

-Size Sheet

Monday, May 8, 2017 2:07 PM

18 components (18 with Part Names) 22 connections in 12 nets

20. Finally, transfer the schematic to PCB through [Design]→Transfer to PCB.

The dialog will automatically use the same *output file* name as the schematic being transferred. Click the [**Browse**] button to enter a different name.

Set the output file to **DesignA1.pcb** as shown →

Choose '2 layer 1.6mm.pcb' as PCB Technology. Click [OK]

As part of the process a report is generated identifying any warnings or errors that may be in the Schematic design.

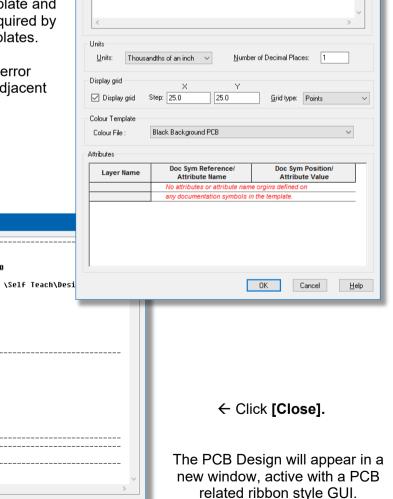

Next specify the PCB design units, Display Grid dimensions, default colour template and enter any initial attribute values if required by your company PCB technology templates.

Once the schematic data is collated error free, you will be prompted with the adjacent dialog. Click [Close]

C:\Users\Public\Zuken\CADSTAR Express

0 Errors,

Collating Schematic Design

CADSTAR Design Editor Version 18.0

0 Warnings

End of report

Close Save As... Print... Copy

New PCB Desig

2 Layer Defaults

**Note:** If you choose the PCB Technology **'1 layer 1.6mm.pcb'** during transfer to PCB, this default technology file is prepared for single sided boards. The advantage of the different technology files is that you still can make use of ONE library as you will experience in Design D.

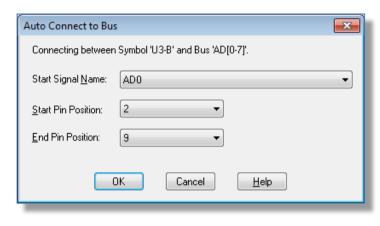

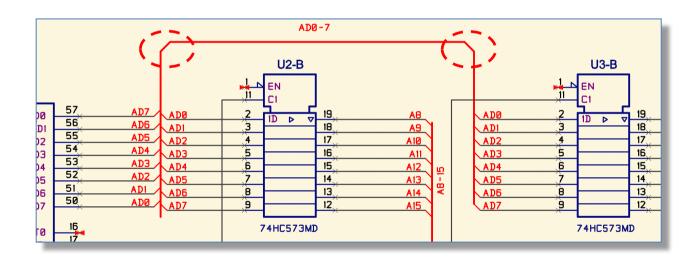

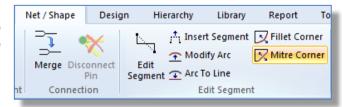

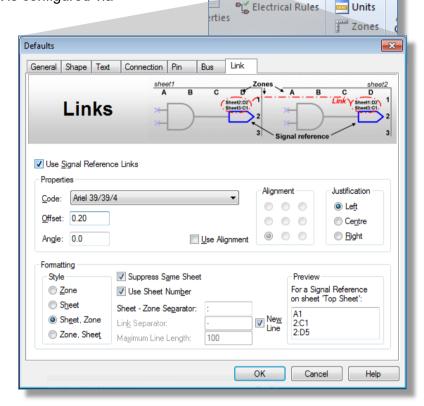

The first steps showed how a schematic design can be drawn for Design A. In fact, any schematic can be drawn following the sequence shown. However, a more complicated design will require more challenging steps. There are many tools within CADSTAR Design Editor that will help designers like you to create a schematic. You can also add spacing classes, insert a component into a net without any disconnection, and perform auto-connection of busses. Other tools like Align Symbol, Design Re-use, Design Variant, Hierarchical Design, etc. are also important and are user friendly for professional design engineers to use.

You can now move on to PCB Design. You will notice that the CADSTAR Library, Schematic and PCB design editor run on the same Graphical User Interface, guaranteeing a fast and problem free transfer.

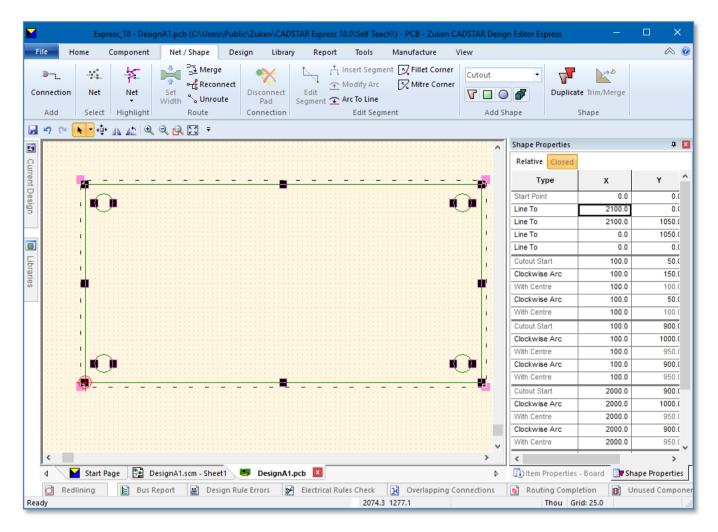

## Step 2 - PCB Placement for Design A

If you didn't create the new PCB design as described, just open **DesignA1\_CS.PCB** and save it as **DesignA1.PCB**

Set the design units to "Thou" (Thousandth of an Inch) by selecting [Design]→Units or alternatively by double-clicking the units Thou Grid: 5.0 at the bottom of the CADSTAR window.

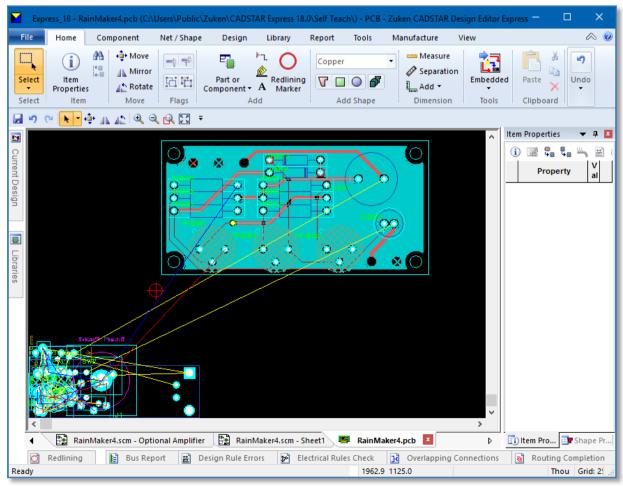

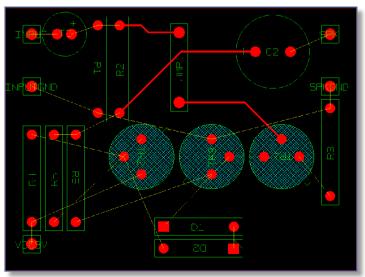

When a new PCB design is created all components are placed in the positive quadrant of 0X, 0Y, this is considered the initial Design origin.

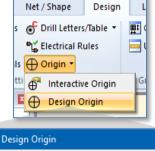

2. Select the [**Design**] tab and click on [Origin → Design Origin].

You will see the design origin symbol at 1000 for both X and Y position. This is defined in the '2 layer 1.6mm.pcb' PCB Template that was used.

Cancel

Help

Net / Shape

Is ⊕ Origin ▼

tti

of Drill Letters/Table ▼

Interactive Origin

ூட் Electrical Rules

Design

u

**⊞**‡

G

Next, you will have to create a PCB outline:

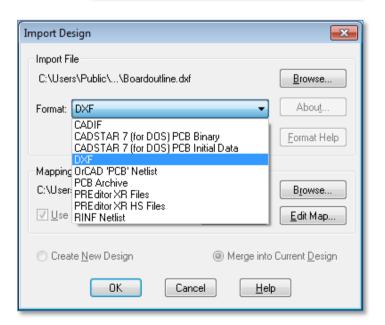

A board outline can either be created within CADSTAR or imported via DXF format.

3. Select [File] tab→File Import. Change the Format to DXF.

Select the DXF file **Boardoutline.dxf**.

For the Mapping-file, you have to select **dxfin.map**, which you can find in the .../user/ folder and just click [OK].

If you have chosen to import the DXF board outline, then skip to step 7.

OΚ

**Note:** the board outline that is imported using the DXF data is different from what is described in step 4. The intent is to demonstrate the support for DXF Line entity styles such as BLOCK, INSERT, ELLIPSE, SPLINE and POLYLINEs.

CADSTAR also supports Importing and Exporting of IDF 2.0 and 3.0 from most mechanical CAD systems.

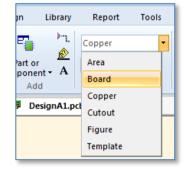

4. Alternatively you can manually draw the board outline.

Let's try to do this by inputting coordinates using a dialog.

Locate the *default shape type quick-pick* menu on the [Home] tab and change the default to **Board** as shown to the right.

Next, click the "Add Rectangle" button.

Click the <**R.M.B.**> and select **Input Coordinates**.

Enter a Width value of 2100. Enter a Height value of 1050.

Leave the other fields as shown >

Click [Apply]

**Note:** if you choose to create the shape without the use of the *Input coordinates* assistant watch the absolute and incremental coordinates at the bottom of the CADSTAR window when drawing the board outline.

**Tip:** From any point in the design you can reset the incremental coordinates by pressing the 'Z' key, followed by the **<Enter>** key.

5. To modify any outline (board, figures, component outlines etc.), simply click on the shape edge and select one of the grab handles. You can also use the Shape Properties panel on the right side of the application window. By selecting the outline you can see and modify the absolute or relative coordinates.

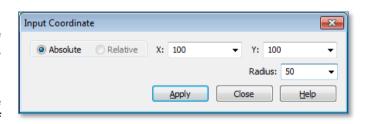

6. You can also create screw holes or mounting holes if you like. To do this within the board outline locate the *default shape type* quick-pick menu and change the default to **Cutout**, and then click any of the drawing tool icons  $\Box \circ \lor \lor$ . In this case you will add four round holes with a 50 thou radius.

Click the Add Circle icon.

Click on the board outline then click the <**R.M.B.**> to select the **Input coordinates** assistant.

Enter X 100 Y 100 as the location of the center of the cut-out and enter a Radius of 50 thou.

Click [Apply]. The Input coordinates assistant will remain open.

Remember to select the board outline before selecting each add shape as per the command line instructions.

If the board outline is in full view you should see the first cut-out in the lower left corner of the rectangle.

Add cut-out number two at X 100 Y 950.

Retrieve the previous radius value of 50 from the pull down list and click [Apply]. The Input coordinates assistant will remain open.

Repeat the sequence for cut-out number three at X 2000 Y 950 and cut-out number four at X 2000 Y 100.

If you didn't manage to draw the board outline or to import the board outline through DXF, just open **DesignA2\_CS.pcb** and save it as **DesignA2.pcb**. Note the board shape is as shown above.

Once the board outline has been imported or drawn manually you can set an interactive origin, to reference all X and Y co-ordinates of all design items, and cursor positions, relative to the new origin.

7. Select **Interactive Origin** from the **[Design]** tab and place the origin at the lower left corner of the board.

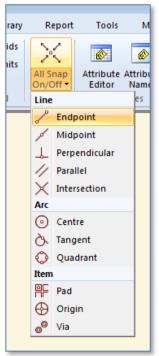

Enable Snap to Endpoint it will be even easier to place the Interactive Origin. To do so select **All Snap on/off** located on the **[Design]** tab.

Net / Shape

s ⊕ Origin ▼

of Drill Letters/Table ▼

Interactive Origin

ବ୍ୟୁ Electrical Rules

ig ( Design Origin

Design

## **Component Placement**

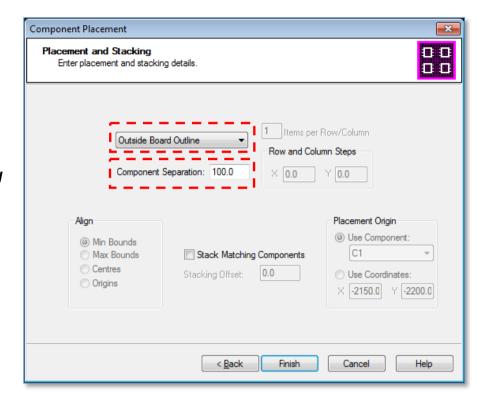

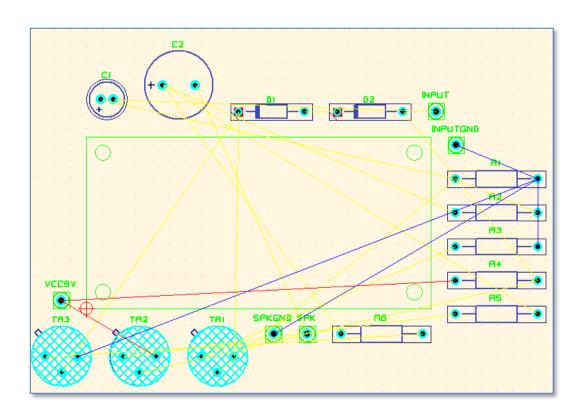

Start by moving or arranging the components around the outside of the board outline.

8. Use the Arrange Components function, located on the [Component] tab to move the components from zero, zero.

Select the *Place around* board outline option on the first dialog and click [Next]..

Set the method to **Outside Board Outline.**

Set the Component Separation to 100.

Click [Finish]

Your results may vary.

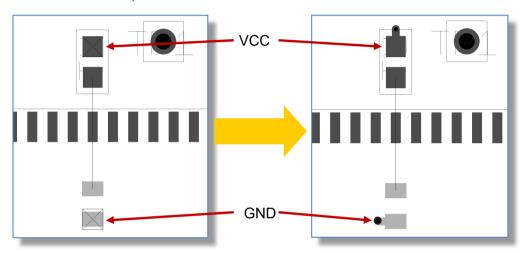

Place the critical components inside the board outline. In this sample design, the SOLDEREYE parts should be placed first. You may consider these components as critical where as their location would be described by mechanical engineers. This is also possible in CADSTAR using the BoardModeler Lite application as well as the IDF Module If you do not have BoardModeler Lite or the IDF Module. You can use the *Item Properties* panel to enter placement criteria such as X, Y Coordinates, Rotation and Board side.

**Note:** BoardModeler Lite and the IDF Module are available for evaluation by contacting your local CADSTAR Sales Agent.

- 9. Open the non-modal *Item Properties* panel located on the right side edge of the application window. Click the pin icon for it to remain open.

- 10. Select component VCC9V by clicking on the outline or just type in "VCC9V<Enter>". (It will be highlighted automatically), then change the X-position to 250,0 and Y-position to 875,0 and click the **Fixed** tick box.. The component will move to the new location. Click in the PCB window.

Repeat this action for:

Component SPKGND, change the X-position to 450.0 and Y-position to 875.0 Component SPK, change the X-position to 650.0 and Y-position to 875.0 Component INPUT, change the X-position to 1650.0 and Y-position to 100.0 Component INPUTGND, change the X-position to 1850.0 and Y-position to 100.0

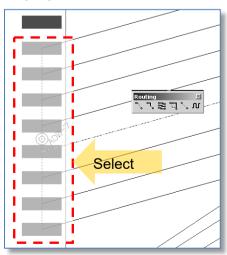

11. Place the remaining components by selecting the Embedded Place and Route icon located on the [**Tools**] tab.

Select the [Home]→Stack off-Board icon.

Enter < Ctrl+A > to select all

components. This will result in all the components that are currently unfixed to be randomly placed around the perimeter of the outline. This serves as a second option for arranging components.

12. Select the **Move** icon and the **Component** mode focus icon.

13. Select component "TR1" and move the cursor inside the board Cancel outline. Click the <R.M.B.> and you will see a list of assist Clockwise commands as shown to the right. > AntiClockwise Swap Align Push Toggle Errors Allowed Ħ2 Toggle Dynamic Pushing VCC9\SPKGND SPK Toggle Move Track INPUTNPLITGNE

Selecting **Clockwise** or **Anti-Clockwise** will rotate the component accordingly. You can do so by pressing '**C**' or '**A**' on the keyboard to gain the same result.

Selecting **Swap** will mirror the component shape to the opposite placement side.

The Embedded Placement tool will aid in error free placement. However, there are times when an error is needed temporarily. Such as, to place a component back outside of the board outline temporarily. This can be achieved by selecting "**Toggle Errors Allowed**".

If the default action is to push other components, the opposite behaviour can be chosen using the **Toggle Dynamic Pushing**.

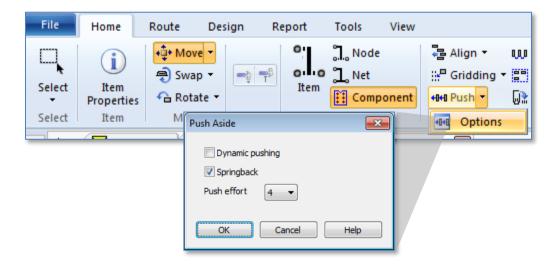

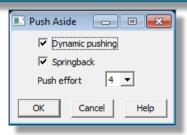

To set the default action, select the **Push** Options dialog located on the [Home] tab

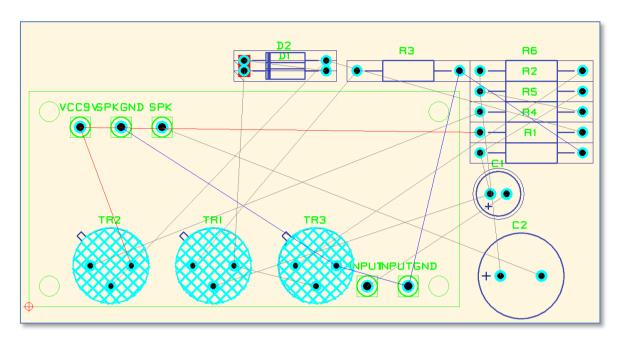

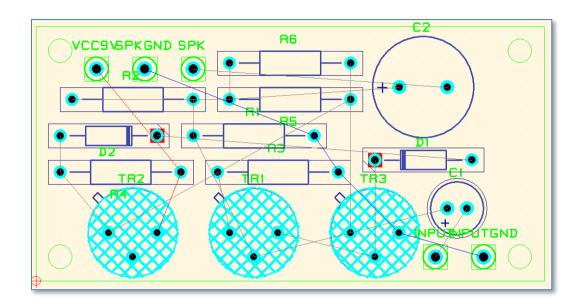

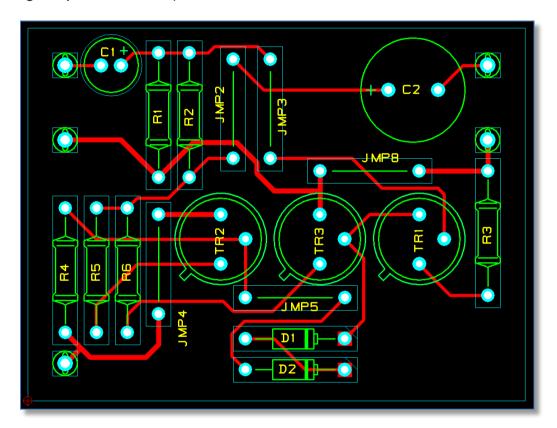

14. Place TR1, TR2 and TR3 like the image below. Practice using techniques to achieve some preliminary results.

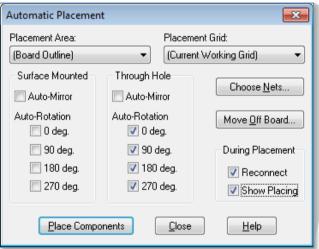

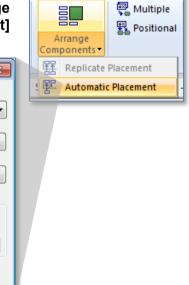

15. After the placement of all critical components and some preliminary placement is complete, exit the Embedded Place and Route Editor and place the remaining components by selecting **Arrange Components**→**Automatic Placement** function on the [Component] tab.

Component

Net / Sha

Enable all Auto Rotation angles before placing the components (depending on your design rules). Try the different settings and experiment with the different results.

Sample placement with only o and 180 degree auto rotations enabled.

If you didn't manage to place the components, just open **DesignA3\_CS.pcb** and save it as **DesignA3.pcb**.

16. Try moving the components manually using a finer working Grid Thou Grid: 5.0 (click on the grid button at the bottom of the window).

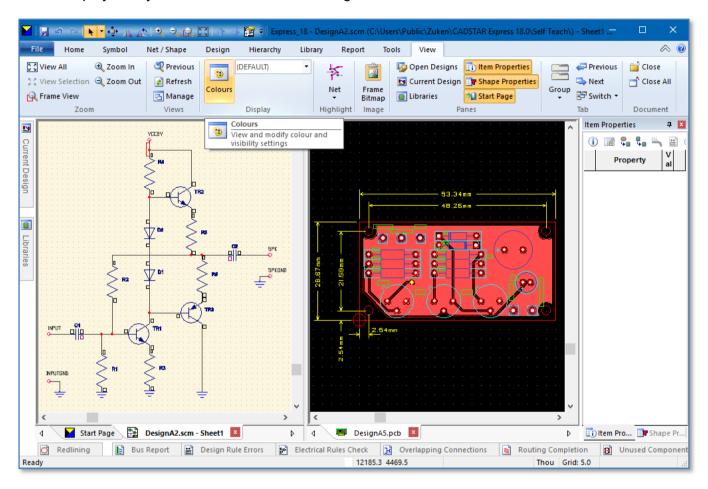

**Note:** you can select any footprint in PCB by simply selecting the particular symbol in the schematic. In CADSTAR, This called *Cross-Probing*. To try it, select **Group→New Vertical Tab Group** located on the **[View]** tab first. Then select any random item.

To continue with the next exercise, you should activate and enlarge the PCB Design window.

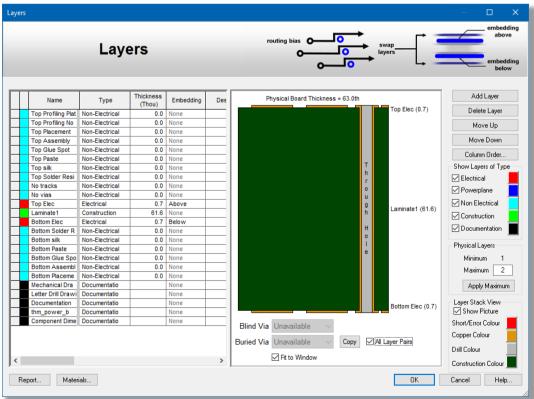

#### **Setting up Powerplane Templates for Copper Pour**

Power Planes are an integral element in the PCB. CADSTAR can accomplish this as a Negative Powerplane where templates can be created on designated Power Plane layers to set the boundary area for split power planes and DRC checking. This then requires a power plane output which is a traditional *negative* photo image output.

Alternatively templates can be created on Electrical layers for use as a positive photo image copper pour effect. This guide will focus on this method as it is the most popular among users.

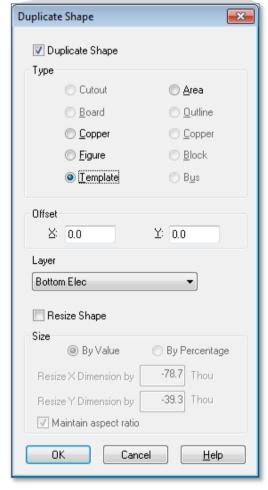

17. To create a partial power-plane, create a template by duplicating the board outline. Select board outline and then **Duplicate** shape function on the [**Net/Shape**] tab.

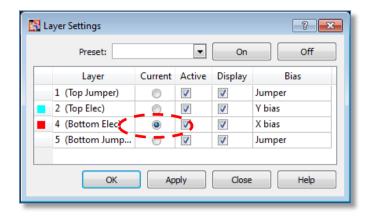

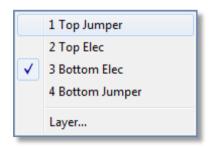

Change the type to **Template** and the layer to **Bottom Elec**.

Disable Resize Shape if selected.

Click [OK] to create the template.

**Note:** Copper pour will be generated automatically in the Embedded Place and Route or stand-alone Place & Route Editor on solder side based on the template area. Copper shapes will be created to fill in the empty space within the template outline connected, for example, to AGND.

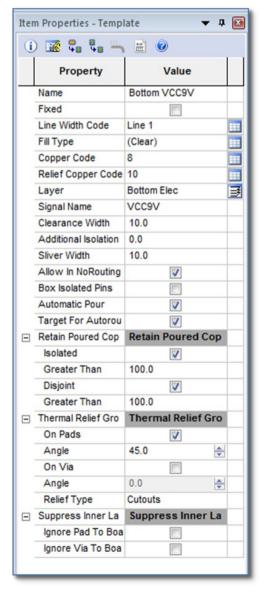

18. After the template has been created you can set the properties to control how copper is generated. Select the template and click on the non-modal **Item Property** panel and pin it open.

**Note:** the demonstration video suggests **Bottom AGND** as a template name with signal **AGND**. Please set the properties as described below.

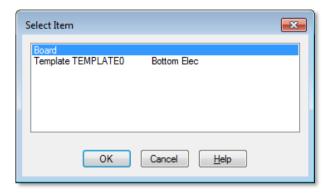

**Tip:** If you are unable to select the template, enable the pick from list function in the **[File]→Options [Interaction]** tab.

With this enabled, select the board shape outline once again. This time a *Select Item* dialog will appear to make it easier to select the template outline.

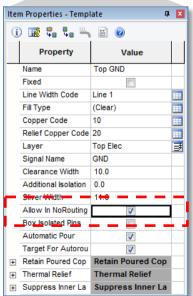

Set the properties as follows:

Name Template: Bottom VCC9V

Relief Copper Code: 10

Layer: Bottom Elec Signal Name: VCC9V Clearance Width: 10 Allow in No Routing [select]

Thermal Relief: Enable On Pads

Angle 45°

**Note:** Automatic Pour is ENABLED!

[These are the important parameters you need to set.]

19. Return to step 18 and repeat the process for the *Top Elec* layer using AGND for the template.

Set the properties as follows:

Name Template: Top AGND

Relief Copper Code: 10

Layer: Top Elec Signal Name: AGND Clearance Width: 10 Allow in No Routing [select]

Thermal Relief: Enable On Pads

Angle 45°

The steps that were mentioned in this chapter are again a typical sequence. There are other tools such as Radial Placement, Gate and Pin Swap, Replicate Placement etc., to help designers achieve correct placement of components.

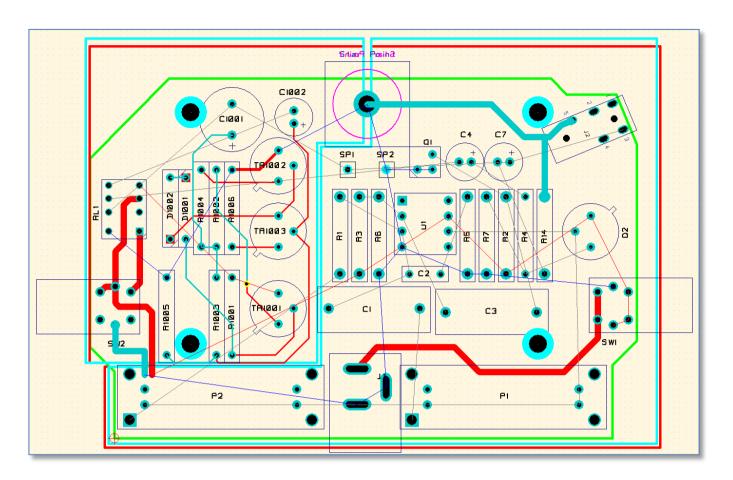

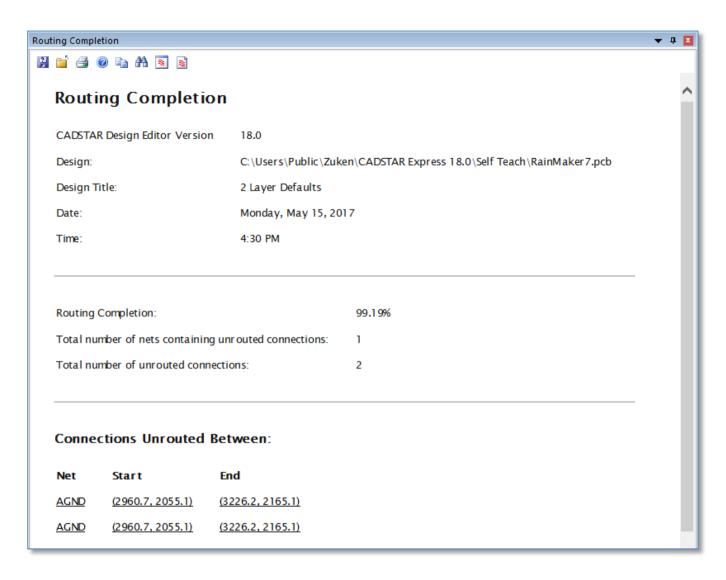

### Step 3 - PCB Routing for Design A

With placement completed we can now start to route the PCB. If you didn't manage to create the template, just open **DesignA4\_CS.pcb** and save it to overwrite your current design before going to the routing environment.

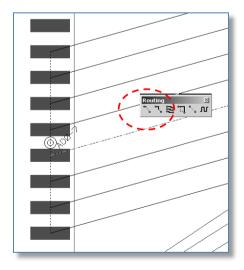

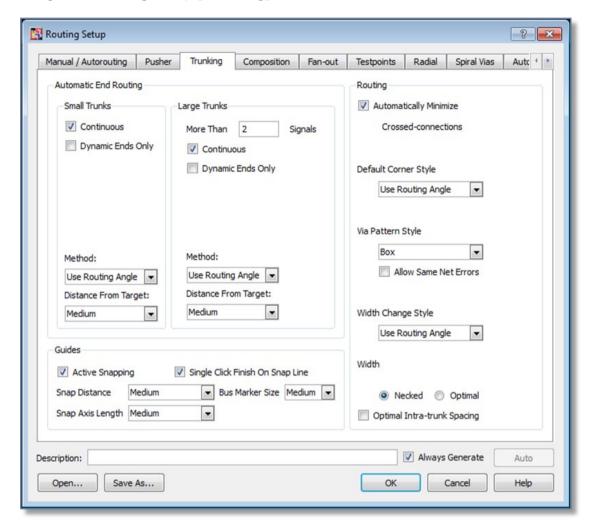

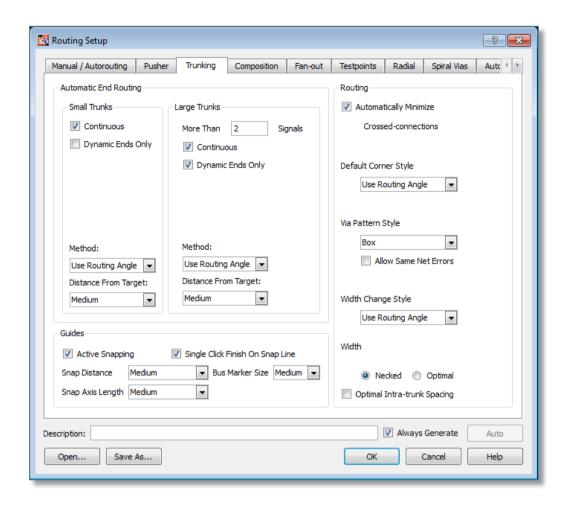

1. Select the [Tools] tab→ Embedded Place and Route, to go to routing environment.

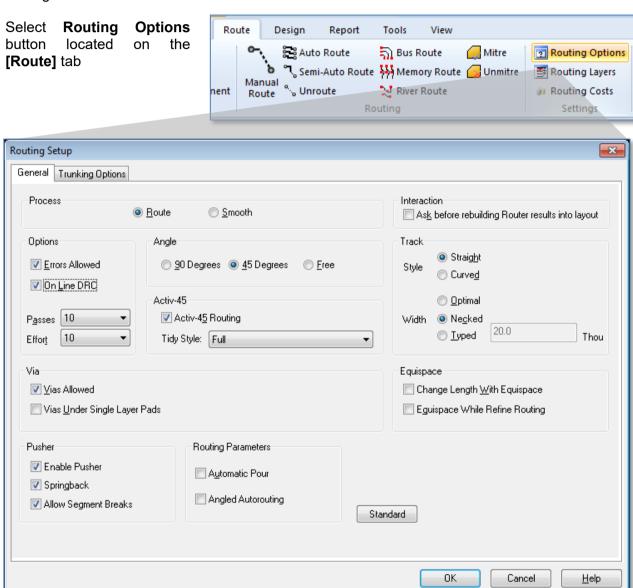

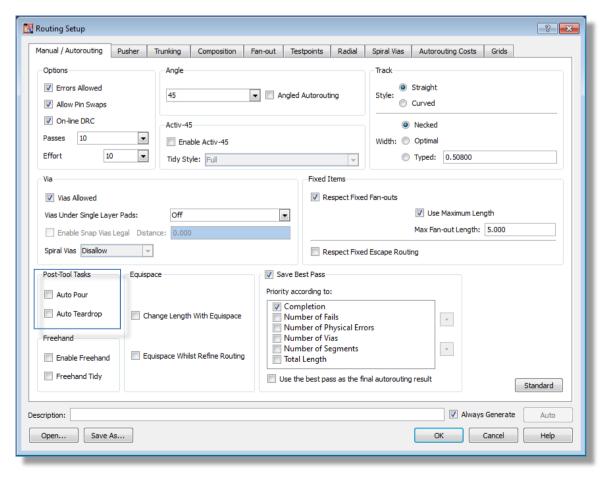

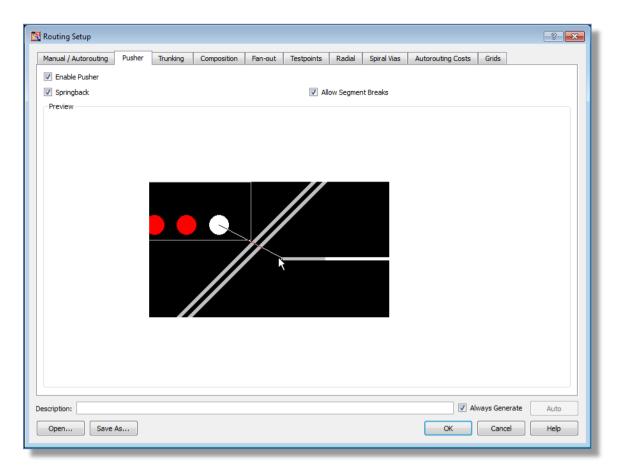

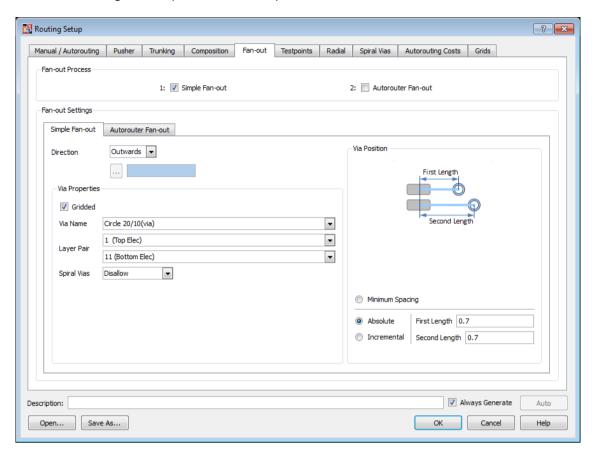

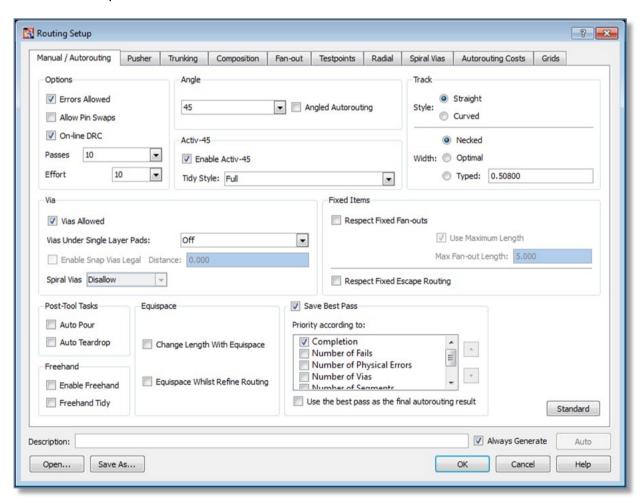

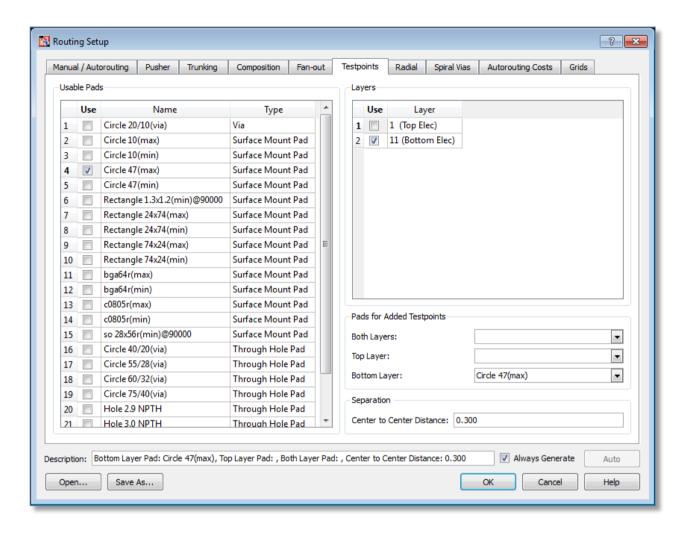

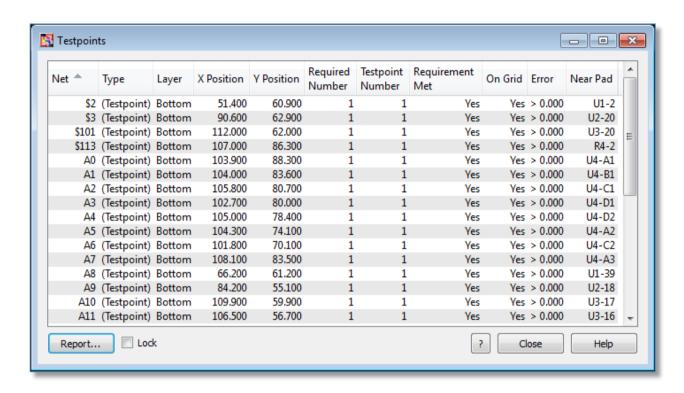

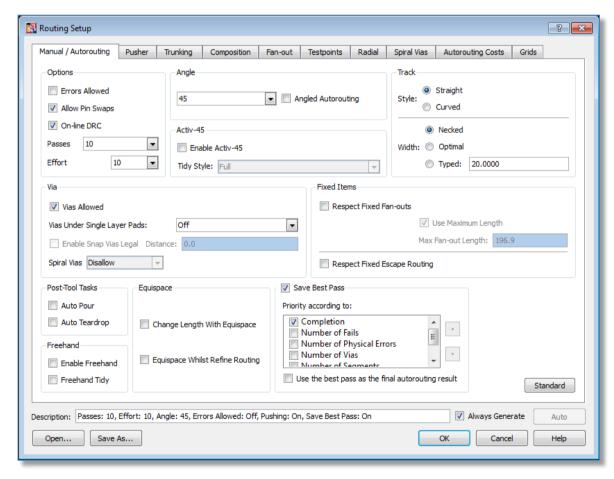

Begin by check the **Routing Options**. Setting the Routing Options is very important before any routing.

The Routing Options dialog contains several options to control routing behaviours:

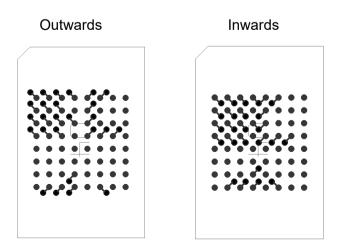

Route Width, Routing Parameters (for autoroute), Routing Angle, On-Line Design Rule Check, Push Aside, Activ-45 Degree Routing etc.

Make sure that at least On-line DRC, Angled Autorouting, Angle 45 Degrees, Activ-45 Degree Routing are *Enabled*. You can use these options to create the result you want.

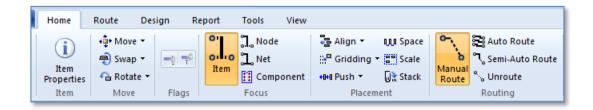

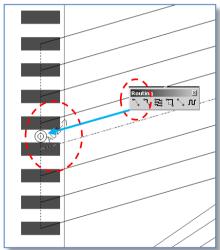

2. Start with manual routing by clicking two icons on the toolbar, **Item Focus** and **Manual Route** located on the **[Home]** tab as shown above.

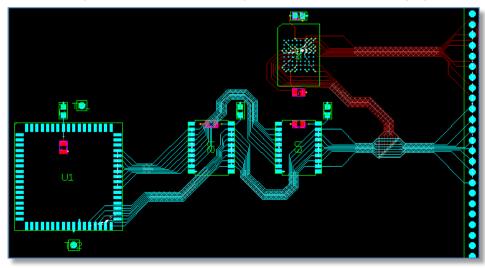

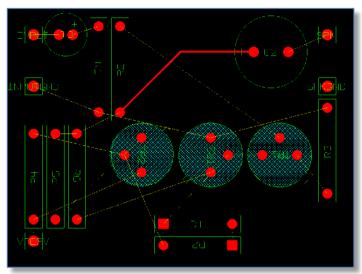

Try out the Activ-45 Degree Routing and Automatic Pour starting on the Solder-side (Bottom Elec), by selecting a net just once and moving the cursor to the other end of the net.

To insert vias, requires the changing of the active routing layer from *Top Elec* to *Bottom Elec* (by clicking the Top Elec button at the bottom of the window and changing the current layer to Bottom Elec).

While routing, you can insert a via by using the right-hand mouse button and select Change Layer.

Route width can be changed *on the fly* from Optimal to Necked or Change Width using the right-hand mouse button and select Change Width (you can choose a width between Min and Max, depending on your Route Assignments).

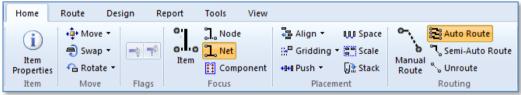

Use the automatic routing features. The two icons used are **Net Focus** and **AutoRoute** shown above. Nets can be automatic routed individually or by dragging a selection frame area around the whole board outline.

Copper pour will be generated automatically on the Top Elec and Bottom Elec layers since you enabled *automatic pour* earlier.

**Note:** the copper poured into the template will have followed the properties you have set. The copper will also have automatically avoided the cut-out of the board outline.

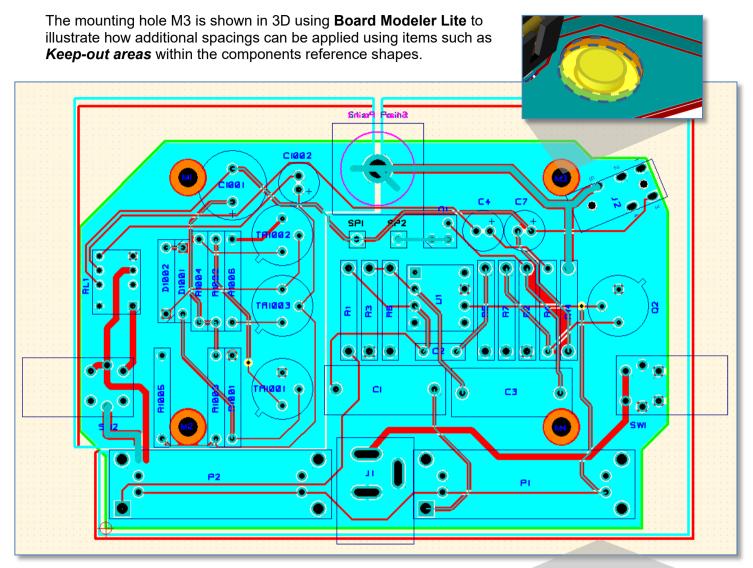

**Note:** Transistors, TR1-TR3 contain a round *Keep-out* area within the component shape, shown as cross-hatched in the previous images. You may choose to change the colour settings so that *component areas* are not visible. The settings for the templates that *Allow in No Routing* areas while be considered resulting in copper being poured within the area. Try it!

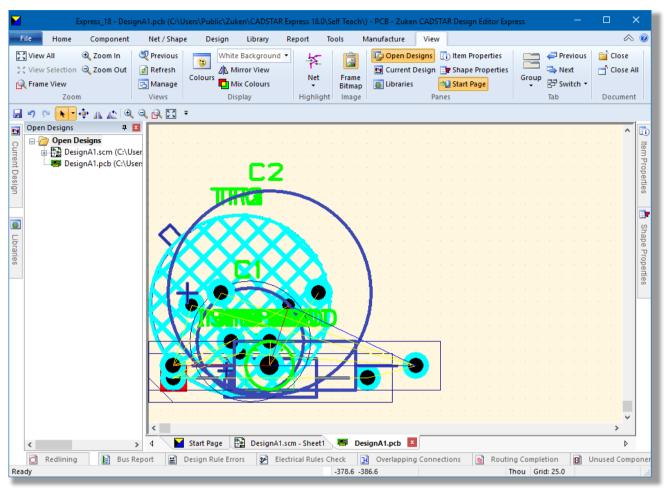

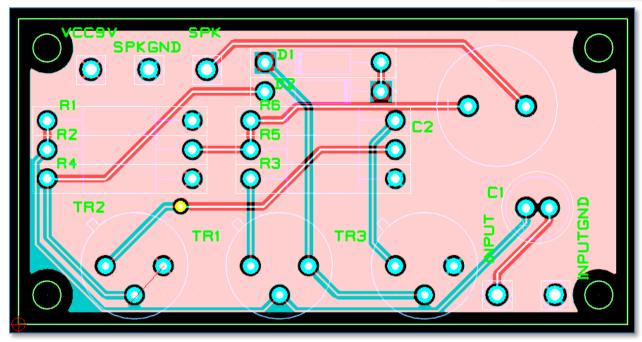

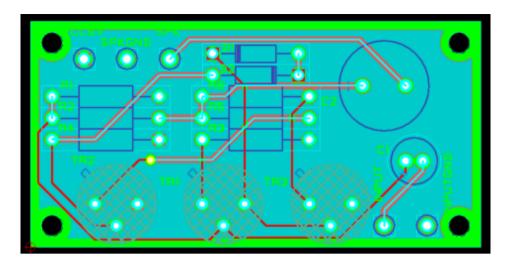

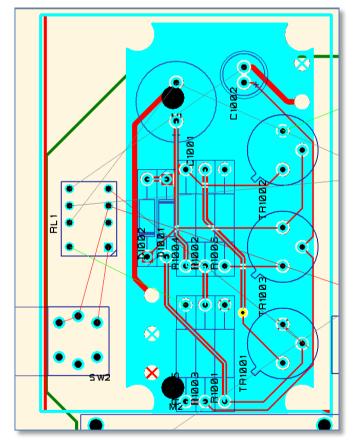

4. After completion, you can go back to the PCB Design Editor window by selecting [File] tab and clicking the Exit Embedded Place and Route icon. Don't forget to rebuild the router results into the layout. You can now see a design similar to the PCB shown below.

5. For a different view of the PCB use the Mix Colours (transparency) mode located on the [**View**] tab This will display multiple layers so that all items are visible. Shown above

Note: This is best viewed using a black background.

- 6. If you required, a mirrored view of the PCB design select [View] tab→Mirror View. This view option allows work to be performed as if you are working on the bottom side of the PCB.

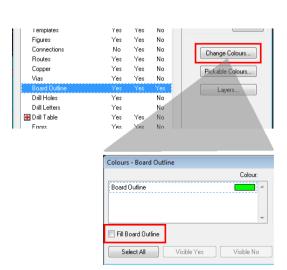

- 7. The board can also be displayed filled. Select [view] tab -> Colours,

Pick the Board Outline category and select **Change Colours**

A checkbox in the Colours – Board Outline dialog allows you to toggle the fill style of the board.

# 8. Save the file

If you didn't manage to route the design, just open **DesignA5\_CS.pcb** to have a look.

This is probably the last stage of the PCB design. It requires some careful considerations as to how the board can be routed, what are the critical nets and what nets have to be routed manually etc. For advanced users, more routing features and high-speed routing are to be considered.

## Step 4 - Manufacturing data for Design A

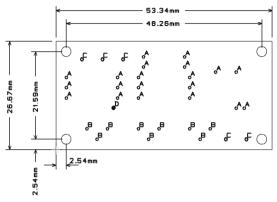

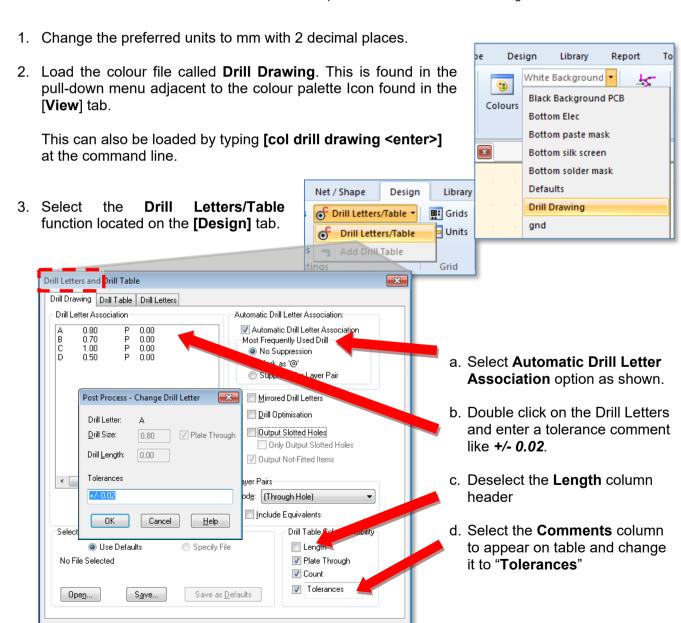

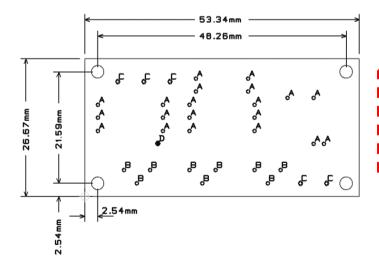

At this stage, you can also create the manufacturing data (Gerber, N.C.Drill, Parts List, Placement data, Drill Drawing, etc.) for the manufacturing of the PCB. Start by creating a Drill drawing with an associated Drill table as shown below. Your design may be different.

|      | Drill Table |         |        |       |           |  |  |  |  |

|------|-------------|---------|--------|-------|-----------|--|--|--|--|

| Size | Plate       | Through | Letter | Count | Tolerance |  |  |  |  |

| 0.50 |             | YES     | D      | 1     | +/- 0.02  |  |  |  |  |

| 0.70 |             | YES     | В      | 9     | +/- 0.02  |  |  |  |  |

| 0.80 |             | YES     | A      | 20    | +/- 0.02  |  |  |  |  |

| 1.00 |             | YES     | С      | 5     | +/- 0.02  |  |  |  |  |

Drill holes marked with letters that correspond to a hole count in a table or legend.

Cancel

Help

OΚ

- 4. Select the [Drill Table] tab.

- a. Change the Layout, layer to Letter Drill Drawing

Selecting the *Show Drill Settings* option will show pertinent settings that are useful for the Fabrication of the PCB. Leave it deselected.

b. Click to [Add Drill Table] button.

This will make the drill table appear on your cursor.

5. Move the table to the right of the PCB board outline and <click> to release it as shown below.

| Size | Plate | Through | Letter | Count | Tolerance |

|------|-------|---------|--------|-------|-----------|

| 0.50 |       | YES     | D      | 1     | +/- 0.02  |

| 0.70 |       | YES     | В      | 9     | +/- 0.02  |

| 0.80 |       | YES     | Α      | 20    | +/- 0.02  |

| 1.00 |       | YES     | С      | 5     | +/- 0.02  |

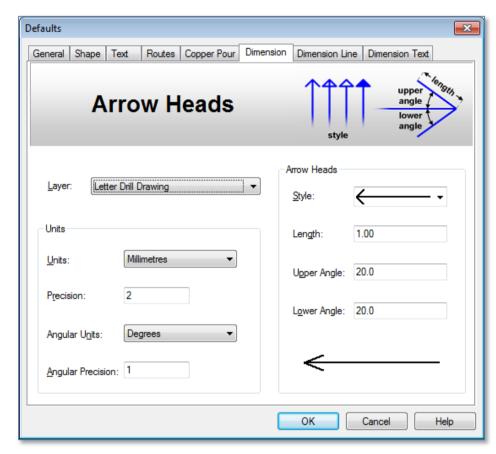

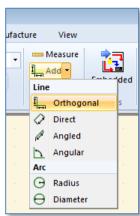

**6.** Try adding dimensions as shown on the previous page by clicking the [**Home**] tab and then selecting the style of dimension you wish to add from in the **Add Dimension** list.

The default dimension styles and details are declared in [**Design**] tab, **Defaults** dialog. Once the dialog is displayed, move the cursor over the various parameters for a graphical representation of the meaning.

TIP: Try using the Snap mode functions located on the [**Design**] tab when adding dimensions.  $\rightarrow$

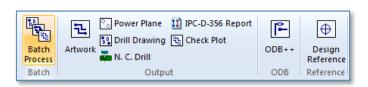

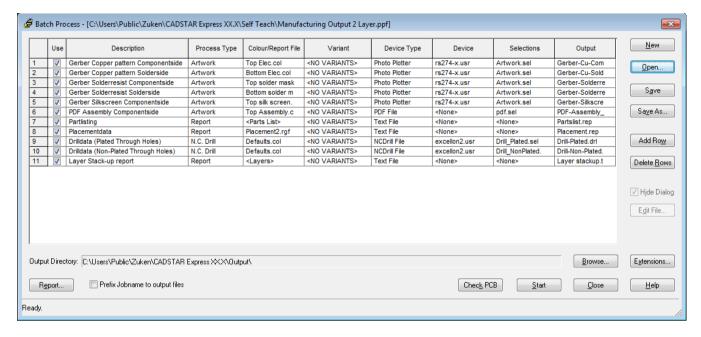

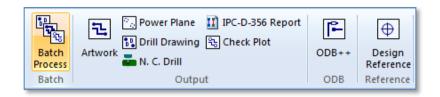

7. Select the [Manufacture] tab and click the Batch Process button on the ribbon.

8. In the Batch Process window, select [Open] and choose Manufacturing Output 2 Layer.ppf, which you can find in the ../Self Teach/ directory.

In this 2 Layer design, the layers that are to be generated are;

- Top Elec

- Bottom Elec,

- Top Solder Mask,

- Bottom Solder Mask

- Top Silkscreen

(all in Extended Gerber RS274-X format).

Additional data generated by CADSTAR manufacturing are;

- Parts Lists,

- Layer Stack-up report

- Placement Data

- Drill Drawings (in the case of this design is recommended to produce PDF artwork of the Drill Drawing layers) rather than let CADSTAR generate a non-WYSIWYG output file.

- Extended Drill Data.

← Click the demonstration video link to see how additional rows can be added such as for a drill drawing PDF file.

9. Click [START]. All manufacturing data will be saved in the Output directory.

**Note:** During the generation of the manufacturing data, a check is performed to ensure items such as Areas, Templates and Component Area are not visible. If they are visible in your design you may receive warnings on rows that are using a colour file. To fix this, exit the **Batch Process** dialog and then load the colour file for the row that is being flagged as a warning. Check the colour file and change the visibility settings to **Off** for the item category being flagged. Return to the **Batch Process** function and click the button to [**Check PCB**]. This is to check the colour files for items that are not normally output as manufacturing details.

**TIP:** Select the Prefix Jobname to Output Files control to append the name of the design to each output file. This makes it easier to keep manufacturing output for different designs in the same folder.

There are other tools such as Associated Dimensioning (Orthogonal, Angular, Radial etc.), Snap, Component Rename etc., to help designers like you to create all the necessary manufacturing data.

**TIP:** CADSTAR also provides Design Rule Check functionality. When you run this function, DRC errors will be flagged in the PCB layout. If you have unresolved errors at the time of post processing, the Manufacturing output will notify you.

### Step 5 – Saving your Design for future Reuse

Small schematic and PCB designs like this Amplifier are typical examples of circuits that are saved for future reuse. Once saved as a reusable circuit they can be recalled for use with other designs. CADSTAR offers functionality for managing *reusable circuits*.

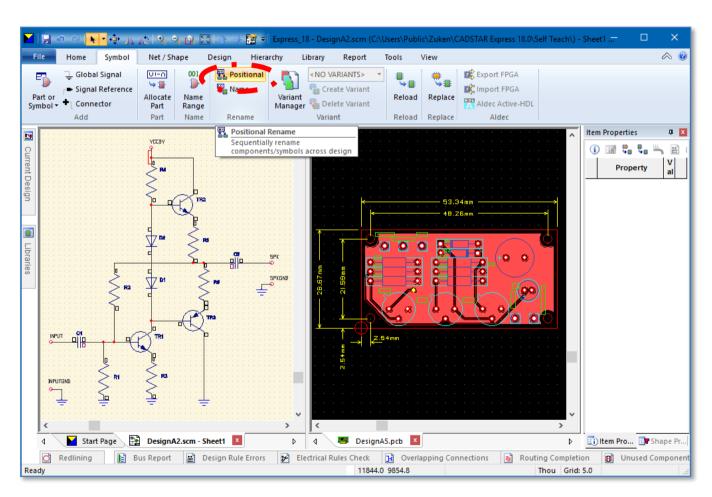

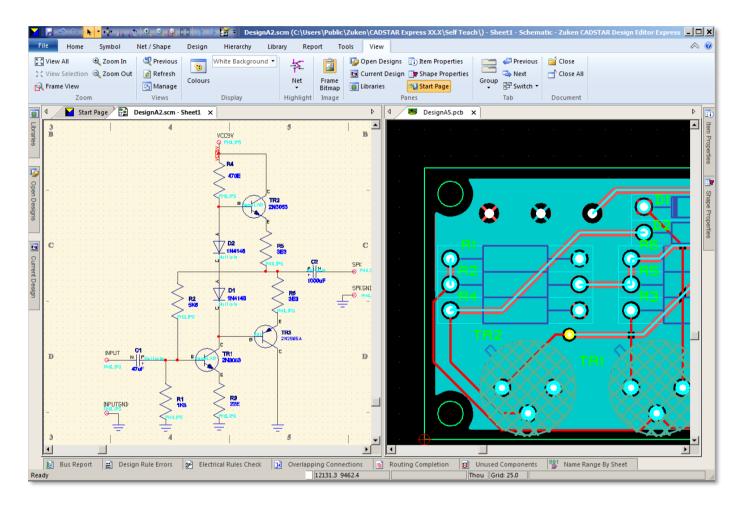

1. Display both your Schematic and PCB Design in CADSTAR.

- 2. Open the *Colour* settings for the design and change the settings for board outline, figures and dimensions to *non-pickable*.

- Select all the electrical contents of your PCB using a simple framing method. If Cross-Probing

is active the same components and nets should be selected in the schematic window. Deselect

the SOLDEREYE parts.

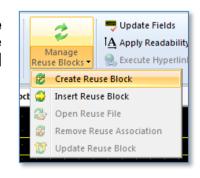

- 4. Select from the [Design] tab Manage Reuse Blocks→Create Reuse Block. The default location for reusable blocks is in the Reuse Files folder as per the Path locations defined in the [File] tab →Options dialog.

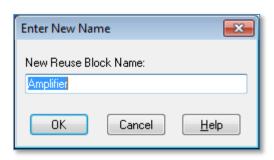

- 5. Choose a valid meaningful name for the file. I.e. "Amplifier" and then click [OK].

- 6. Enter the same name for the Reuse Block name and then click **[OK]**

- 7. With the schematic data still selected from cross probing, carefully click the schematic window tab. (not within the window since this will deselect the contents). This will change the tool ribbon used for schematics. Reselect the circuit block and select [Design] tab Create Reuse Block.

If you have prematurely clicked and deselected the circuit repeat the process for the schematic data. Give the schematic reuse block the same name as the PCB reuse block i.e. **Amplifier.scm. Do not include the SOLDEREYE parts.**

8. Select the Manage Reuse Blocks button. The new block name will be listed. Manage Reuse Blocks -Reuse Reuse Block Manager ж Block Name Item { All Reuse Blocks File path 200 Amplifier Settings Remove Reuse Block ✓ Grouped Fixed Mirrored Orientation: 0.0 Rename... OK Cancel Help

**Note:** Since the Reuse Block files are named, this functionality will allow you to manage them within the \Reuse Files\ folder. If you decided to make changes to the blocks, update both the Amplifier SCM and PCB files. Then, for any design that used the Amplifier circuit, you can simply update them by double clicking on them and selecting the **Actions – Update** option shown above.

In the next project, Design B, the Amplifier reuse blocks will be used. Simply select from the [Design] tab, Manage Reuse Blocks →Insert Reuse Block and select Amplifier.

# Assigning Unique Reference Designators for Reuse Circuits

Before reusing these circuits we recommend you perform a reference designator *renaming* procedure. This will assign unique reference designators to the schematic and PCB components used in the reuse circuits blocks and will also help to eliminate the chances they will be renamed automatically by CADSTAR when they are inserted as reuse circuit blocks.

For instance; When inserting a reuse block into a schematic or PCB that may already have used the reference designators that are used in the reuse definitions, CADSTAR will resolve the duplicate reference designators automatically by renaming them to the next available ref des. This can cause the reuse circuit blocks to become out of synch in between the schematic and PCB reuse blocks.

An elegant solution is to use the rename component function to rename the used reference designators to something with a higher level prefix. I.e. R1  $\rightarrow$  R1001, C1  $\rightarrow$ C1001.

9. Open the **Amplifier** Schematic and PCB so you can see both at the same time and then click in the schematic window to make it active.

10. Select the Positional Rename button on the [Symbol] tab as shown above.

11. Apply the settings as shown in the image for components with a stem name of R.

13. Click in the PCB window for the Amplifier to make it active.

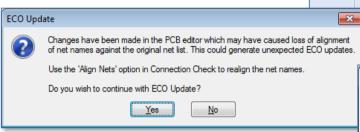

14. Click on the [Design] tab and then the ECO **Update** button.

Click [Yes] if the following dialog appears.

Design

ules

Library

Report

Tools

Manufacture

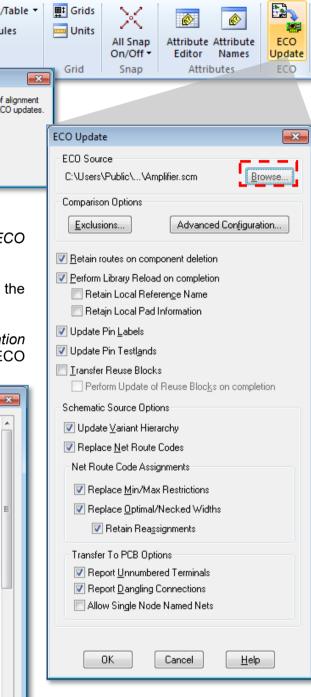

- 15. Browse to the \Reuse Files\ folder and select the Amplifier.scm as the ECO Source data.

- 16. Apply all other settings as shown and click the [OK] button.

- 17. Click [Yes] on the Design Comparison information dialog. The results will be displayed in an ECO Update report

Note: ECO Update will also change system assigned net numbers as part of the process. If you have important nets it is recommended they be given proper names.

18. After reviewing the report carefully, click the **[Close]** button. You will be presented with opportunity to accept the changes. Click **[Yes]**

The PCB design will now be updated to match the schematic.

19. Save the Amplifier PCB design again, overwriting the version currently in the \Reuse Files\ folder.

# This completes the first design with CADSTAR Express!

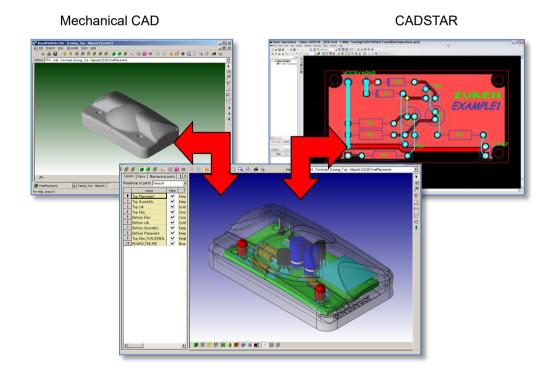

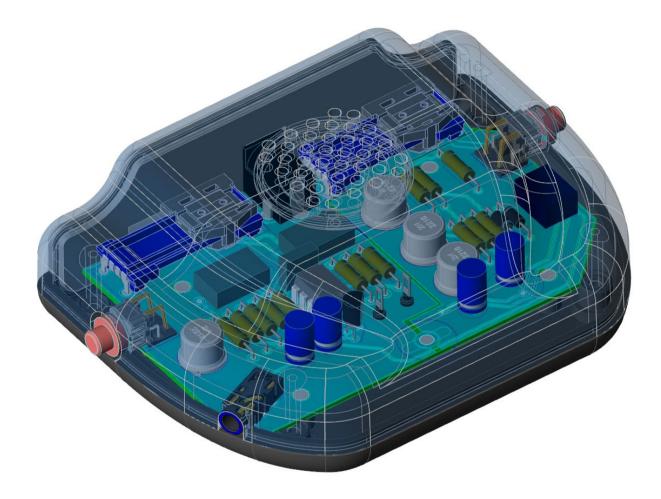

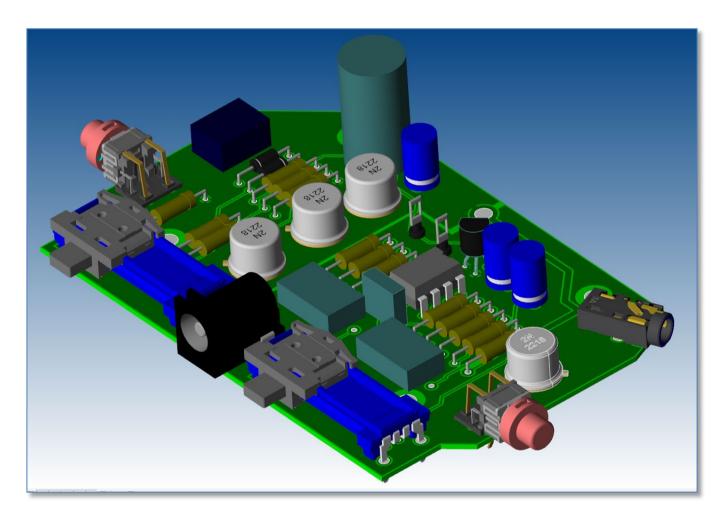

### Add the Power of 3D to your Design

You can also check out BoardModeler Lite, supporting import/export of STEPS AP203, AP214, ACIS,STL and IDF formats, providing you an optimized solution for the placement and verification of a PCB Design in its own 3D environment, including:

a. Replacing board shapes and modifying component placements which are smoothly back annotated.

b. Creating detailed 3D models using the 3D parts creation wizard

c. Importing Mechanical Enclosures (or other PCB designs).

d. Measuring Distances and Checking Clearances.

e. Running Batch collision checks.

#### BoardModeler Lite is more than just a 3D viewer!!!

You can find more information at:

https://www.zuken.com/en/product/cadstar/bundles/

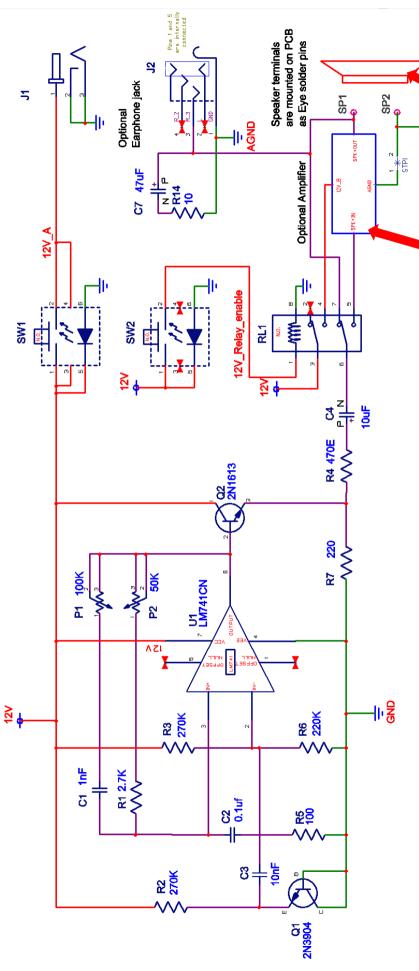

### Chapter 2 – Design B

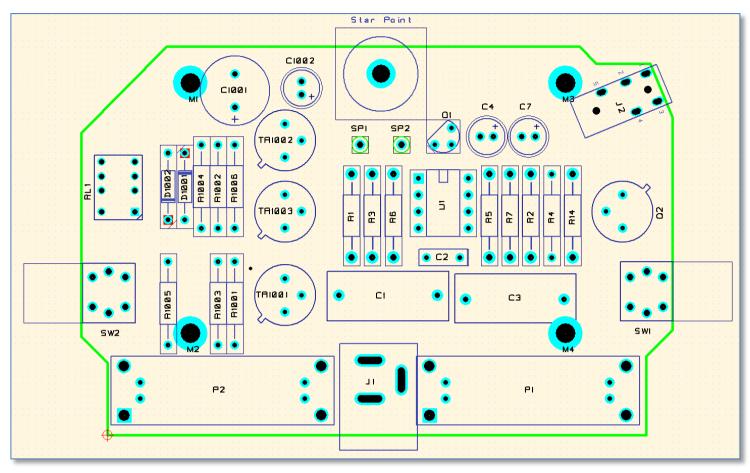

In Design B, we will expand on what you have learned in **Design A** by exploring more features within CADSTAR. We will use the Amplifier circuit in the form of a Reuse Block for both the schematic and the PCB design. We will use Hierarchical features in the schematic and use a more elaborate PCB board outline with predefined component placement as an example of a Mechanical CAD driven system.

The project we will be designing is an audio device that many electronic hobbyists have built to cure insomnia. The circuits will emulate the sound of rain falling. This is similar to that of a white noise generator.

The original circuit was obtained from www.electroschematics.com as a free download.

We have expanded on this by adding an additional amplifier that will be activated with the push of a button and an optional ear phone jack.

The PCB design will be created for you with predetermined coordinates and rotations of the parts. You will import this as a DXF file and begin placing the remaining parts.

Routing and Placement can be accomplished using the Embedded Place and Route Editor.

You will then be able to use your new skills from the previous design to complete Design B called *Rainmaker*.

The Image below contains the finished Rainmaker PCB design. The 3D models are available as part of the CADSTAR – Board Modeler Lite tutorial guide. If you would like to take this project to the 3D Level contact your CADSTAR Sales agent to obtain a full CADSTAR and Board Modeler Lite evaluation license.

### **Step 1 - Schematic for Design B**

The sequence steps are the same as Design A.

- 1. Create a new schematic sheet using **Form A3-euro**. Set the working grid to **thou** and screen grid to **100, 100.**

- 2. Pick out components from the Library Workspace window. You may also use the Library Searcher as well.

The Parts list is as follows

| Part Name           | Description                             | Qty | Comps. |

|---------------------|-----------------------------------------|-----|--------|

| 0.1UF-COG2-5%       | 0.1uf 100V COG Mlayer Ceramic           | 1   | C2     |

| 10-TR4-1%           | 10 Ohm TR4 Metal Oxide Film 1%          | 1   | R14    |

| 100-TR4-1%          | 100 Ohm TR4 Metal Oxide Film 1%         | 1   | R5     |

| 10UF-10V-EC         | 10uF 10V Electrolytic Capacitor         | 1   | C4     |

| 2.5MM PWR CON       | Power supply connector 2.5mm            | 1   | J1     |

| 220E-TR4-1%         | 220 Ohm TR4 Metal Oxide Film 1%         | 1   | R7     |

| 220K-TR4-1%         | 220K Ohm TR4 Metal Oxide Film 1%        | 1   | R6     |

| 270K-TR4-1%         | 270K TR4 Metal Oxide Film 1%            | 2   | R2-3   |

| 2K7-TR4-1%          | 2.7K TR4 Metal Oxide Film 1%            | 1   | R1     |

| 2N1613              | SABER TRANSISTOR                        | 1   | Q2     |

| 2N3904              | SABER TRANSISTOR                        | 1   | Q1     |

| 47uF-10-EC          | 47uF 10V Electrolytic Capacitor         | 1   | C7     |

| 470E-MRS25-1%       | Metal film resistor MRS25 470E 1%       | 1   | R4     |

| BA156K0103J         | Leaded film capacitor                   | 1   | C3     |

| BA156K0104J         | 1nf Leaded film capacitor               | 1   | C1     |

| LM741CN             | SINGLE OPERATIONAL AMPLIFIER            | 1   | U1     |

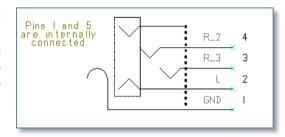

| LGY2109-1701F       | STEREO- CONNECTOR - EARPHONE            | 1   | J2     |

| NEC_TOKIN_UC2_RELAY | / NEC TOKIN's UC2 Mini Signature relay  | 1   | RL1    |

| RS15H11AA04M-100K   | Slim Slide(Slim 4) RS**H Series 100K    | 1   | P1     |

| RS15H11AA04M-50K    | Slim Slide(Slim 4) RS**H Series 50K     | 1   | P2     |

| SOLDEREYE-1MM       | Soldereye 1.0 mm                        | 2   | SP1-2  |

| TL1250F180BQRCLR    | SPST - Tactile Switch N.O with Blue Led | 2   | SW1-2  |

3. Place the components on the schematic sheet. The schematic is on the next page for reference. Feel free to print the page for this easier viewing.

Remember that symbols may be mirrored as well as rotated. However for most cases use the appropriate alternate symbol to match the schematic.

Parts **STP1** is a 2-pin Star point symbol. It resides in the library and has a PCB star point footprint representing a large single pad component. In fact this is special component that allows two nets such as ground returns to be connected together at a predetermined location using routed traces.

The red symbol is created out of figures and grouped together to represent a speaker. The actual speaker for this project is not mounted on the PCB. Only the Solder eye terminals are used.

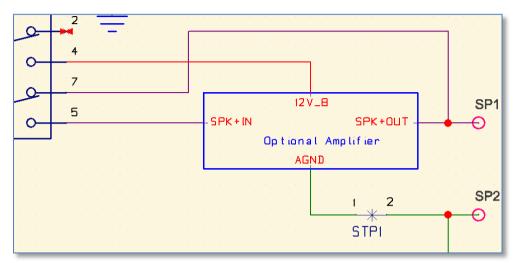

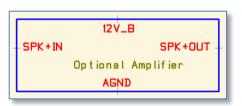

The block shape shown as **Optional Amplifier** is a Hierarchical Block. This will be covered in a later step.

As you create the schematic, feel free to make adjustments to the;

- scale of the symbols using the Item Properties dialog

- size of the text and fonts using the Assignment settings

- position of the attribute test introduced with the part.

- colours using the Colours dialog.

- local visibility of pin names/identifiers for parts such as resistors and non-polarized devices

- 4. Save the design as Rainmaker1.SCM

- 5. Connect the components Note that the connections are different colours. This is due to the use of different route codes.

For Power Nets (red) use

For Ground nets (green) use

For all other nets (purple) use

Net Route Code VCC

Net Route Code GND

Net Route Code GND

Net Route Code Signal

- 6. Add Global Signal symbols accordingly. They can take on unique net names. See the schematic for the appropriate names.

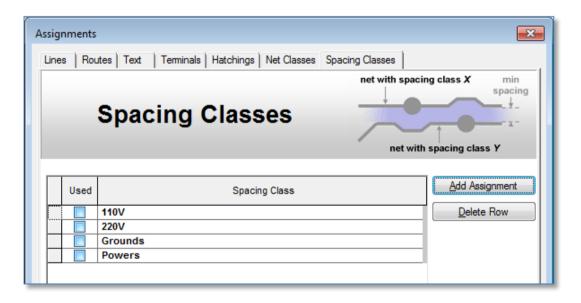

- 7. Optional step. If you would like to learn about using Spacing classes, you will find it very useful to declare unique spacings between groups of Nets. Circuit designers appreciate being able to define this information in the schematic.

8. Save the design as Rainmaker2.scm

We will now add a second sheet to this design. This will be a lower level hierarchical sheet that we can *push down* to and *pop up* from as we move from sheet to sheet. To connect to the sheet we will add a hierarchical block with terminals to emulate signals connected to the lower sheet. The signals names are shown below in red. The block has been named "Optional Amplifier"

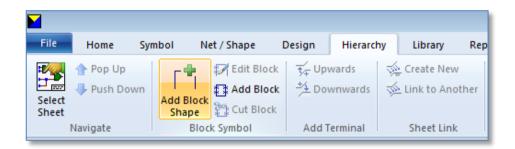

- 9. From the **[Hierarchy]** tab select **Add Block shape**. Click to start the rectangle start and end position in the approximate location shown in the image above.

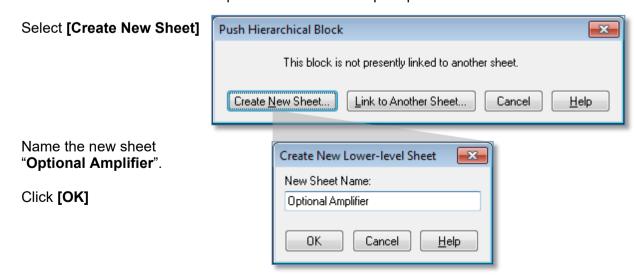

- 10. Double Click on the block shape outline. You will be prompted as follows.

You are now in a new schematic window using the same format sheet symbol labelled Sheet **2 of 2**.

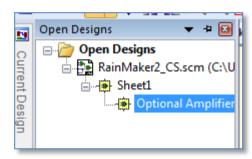

11. Open the **Open Designs** auto-hide panel to see that the new sheet appears indented to suggest that it is a child sheet of the **Sheet1** parent.

**Note:** Here you may rename **Sheet1**, if you wish by clicking on the name and clicking the **<R.M.B.>**. Select **Rename sheet**.

**Note:** New Sheets may be added in this same manner by selecting **Add Sheet.**

Top Level Sheet will be at the same level as sheet 1.

Adding a *Lower-level Sheet* will create it as an *unconnected* sheet and be displayed as a light blue icon. This means that a Hierarchical block will be needed to bring the new child sheet under the desired parent sheet.

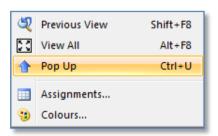

12. Click inside of the **Optional Amplifier** sheet space and the click the **<R.M.B>**. Click the Pop up option to take you upwards to the parent sheet.

This function as well as **Push Down** or doubling clicking on the hierarchical block shape makes it easy to move from sheet to sheet.

Next we will add terminals to serve as connection points to emulate net connectivity between the sheets.

**Note**: that this is optional as common signal names are automatically merged during the *sheet collating* phase, such as during the transfer to PCB process, ECO update and Back Annotation, etc.

13. Click the **Downwards** option on the **Add Terminal** section of the **[Hierarchy**] tab.

Design Hierarchy

Upwards

Downwards

Add Terminal

**Note:** Steps are dictated for functions at the lower left corner of the application window.

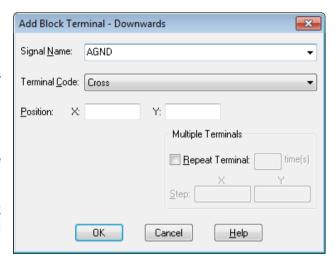

Click on the block shape. From the dialog, open the Signal Name list and select AGND.

Change the *Terminal Code* to **Cross**. This terminal code uses a 'Plus' shape.

Click [OK].

Place the terminal on the bottom side of the block outline as shown.

Press the **<esc>** key on the keyboard or click the **<R.M.B.>** and select **Cancel**. This will return to the dialog.

You may specify new net names as well.

Enter the signal name 12V\_B then click [Ok] and position this terminal on the top of the block symbol as shown.

Repeat for **SPK+IN** and **SPK+OUT** placing them as shown.

Click the <R.M.B.> and select Finish.

You may position the terminal name labels as you like.

14. To apply a name to the block symbol select the outline and enter **Optional Amplifier** as shown and click **[OK]**.

15. **Push Down** to the Optional Amplifier sheet to see the lower level terminals. As each terminal was placed, its corresponding hierarchical terminal was placed at the same X, Y location on the lower sheet.

**TIP:** As the demonstration video shows, Hierarchical terminals codes can be changed, if so desired, using the Item Properties panel. For instance the Hierarchical terminals on the lower level sheet can be assigned a terminal code that represents a filled arrow whereas the Upper hierarchical terminals may continue to use the Cross terminal code.

16. **Pop Up** to Sheet1 and finish adding the connections to the new hierarchical terminals as shown on the schematic. Remember to set the Route Codes to maintain the same colour correlation.

17. Save the design as Rainmaker3.scm.

We are now ready to add the reusable circuit block that we saved in chapter 1.

Creating lower level circuit blocks for the purpose of adding reuse blocks is a nice way to maintain a tidy design flow, though they are not required.

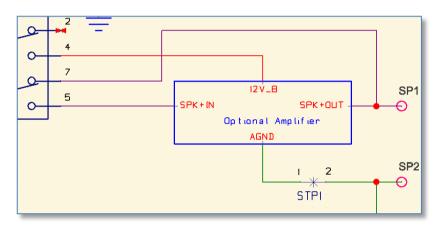

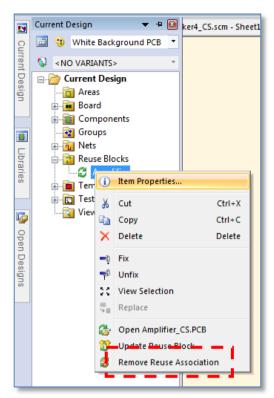

18. **Push Down** into the lower level sheet.

19. From the [Design] tab select Manage Reuse Blocks → Insert reuse Block.

Select the Amplifier schematic block.

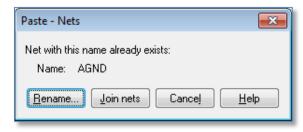

As the block is integrated into the main design items such as component reference designators and net names are checked and compared to those already used.

Duplicate component names are renamed to the next available reference designator per their prefix stem name.

Duplicate Net names are prompted with the adjacent dialog allowing the user to decide to *Join* the nets or *Rename* them to keep them separated.

Manage

Reuse Blocks

Create Reuse Block

Insert Reuse Block

Remove Reuse Association

Update Reuse Block

Update Fields

A Apply Readability

Execute Hyperlin

Since you have connected the AGND hierarchical terminal to the starpoint part, the net does in fact exist and we can Join this instance. Click **[Join]**

The following dialogs are very important to consider. If you are familiar with every net name in both circuits and agree that it is ok to repeat the **Join** operation for every duplicate net then do so. Else you may cycle through each net individually to avoid joining two nets together accidentally.

20. The Amplifier circuit is now attached to your cursor. Place it on the sheet.

The circuit is now grouped and in a state of being locked as a reuse block.

- 23. Create the Parts List When prompted select both sheets in the dialog.

- 24. Print the design.

- 25. Save the design as Rainmaker4.SCM

If you have not completed the design to this point, please load **Rainmaker4\_CS.scm** and save it as **Rainmaker4.scm**.

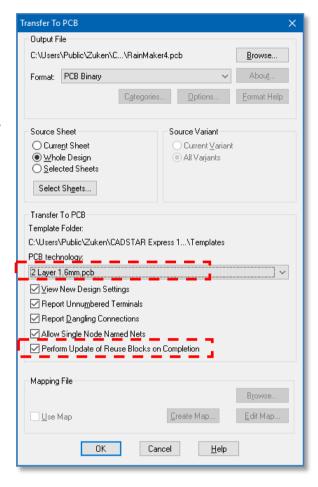

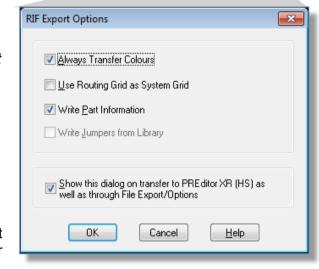

Transfer the schematic design to PCB (choose '2 layer 1.6mm.pcb' as PCB technology).

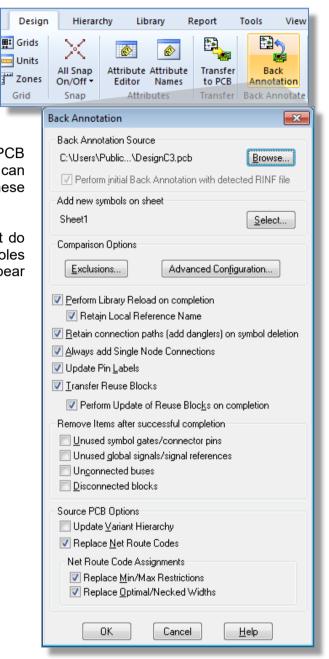

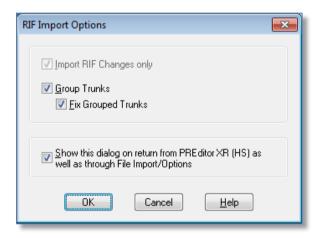

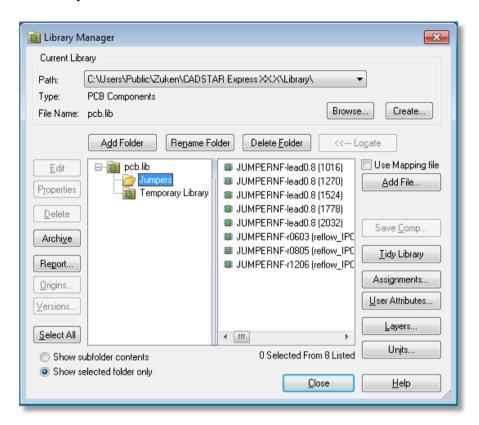

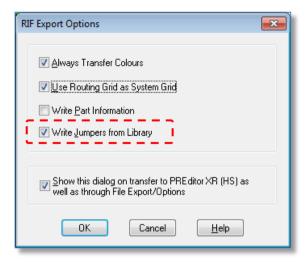

Since we are using design reuse blocks you must also check the option (shown below)

Perform Update of Reuse Blocks on Completion.

You will be presented with several verification dialogs pertaining to new items to add to the design.

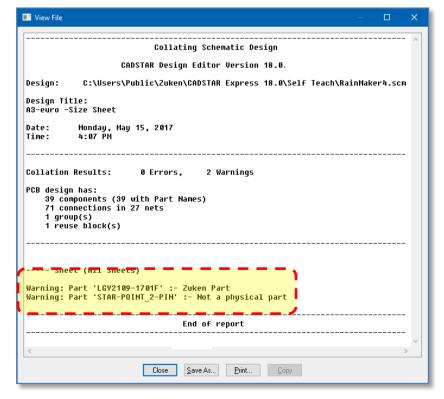

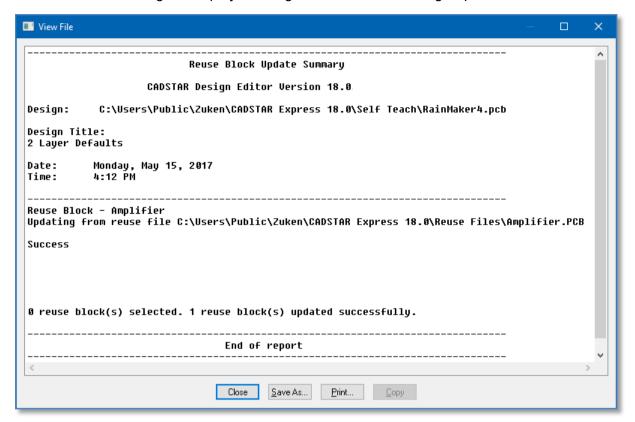

Accept them until the **Reuse Block Update Summary** report appears as shown. →.

**Note:** the warning reflects the use of the *Part Acceptance* attribute used in the parts library definition for:

"LGY2109-1701F" and "STAR-POINT\_2-PIN".

For these parts the text string values have been highlighted for this attribute. You will learn more on this in the next chapter.

Click [Close]

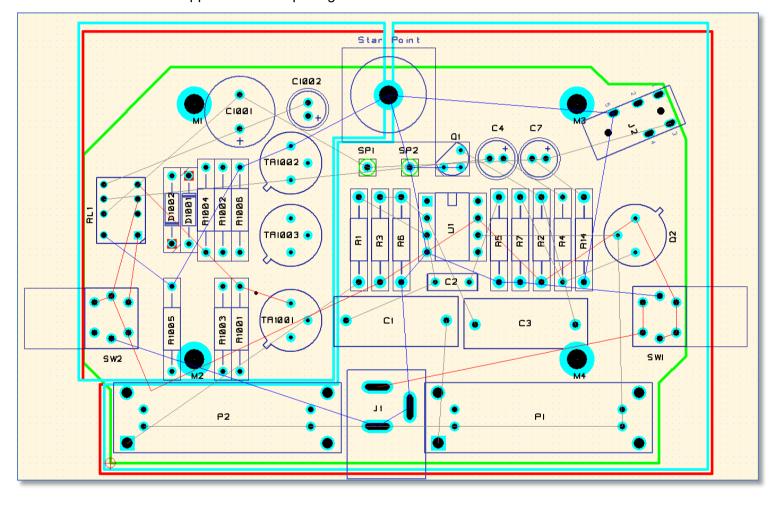

The new PCB design is displayed along with the reuse block, grouped, as shown below.

Note: the reuse block has been moved slightly by the author from its original location for image clarity.

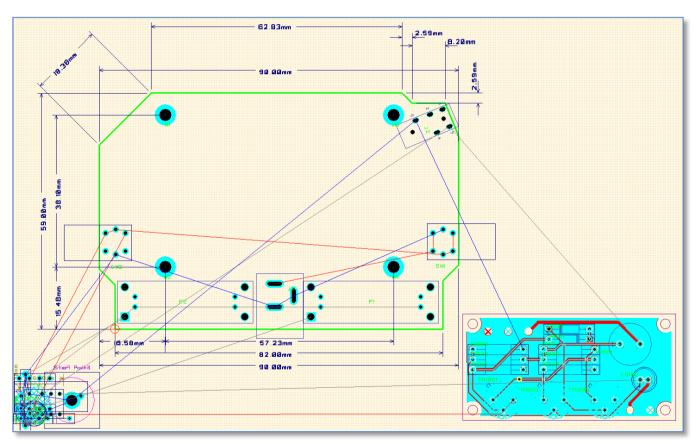

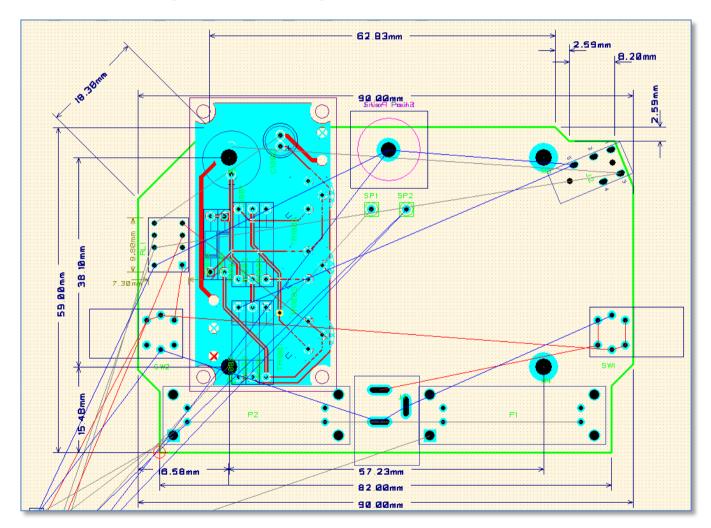

### Step 2 - PCB Placement for Design B

You can now start to place and arrange the components on the PCB after the transfer. If you have not completed the design to this point, please load **Rainmaker4\_CS.PCB**, save it as **Rainmaker4.pcb** and skip to Step 5.

- 1. Check and/or change the Units & Grid (25 thou is preferred).

- 2. Click on the Amplifier circuit block and move it to the right of the components to make way for the incoming board outline.

Remember, when a new PCB design is created all components are placed in the positive quadrant of 0X, 0Y, this is considered the initial Design origin.

3. Select the [Design] tab and click on [Origin→Design Origin].

You will see the design origin symbol move to X 1000, Y 1000.

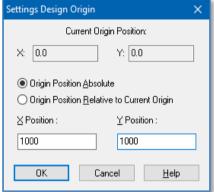

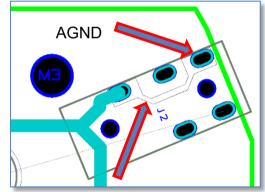

4. Import the DXF Board outline using the Rainmaker\_Boa.dxf file located in the \Self Teach\ folder. Also use the same dxfin.map file. This DXF file also contains other information such as Critical Component placement and dimensions as if provided from the mechanical engineer.

**Note:** From the image above, 4 critically placed components have been added to the design. This refers to 4 mounting holes that are imported as single pad components. The DXF Import process will acknowledge the ref des and component reference shape request. If it is not in the design, CADSTAR will import it from the Parts library. This process is described fully in the CADSTAR Help.

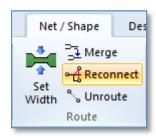

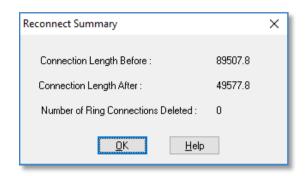

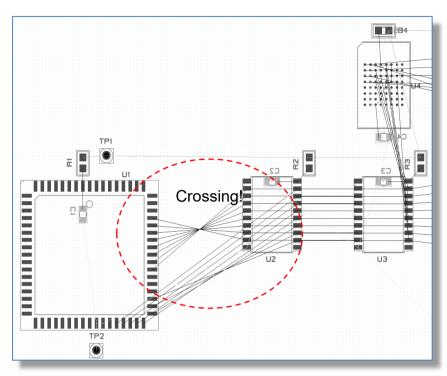

**Tip:** Once the PCB window displays all of the information from the DXF file, you may find that the connections are not optimized (to their shortest length). This can be quickly resolved using the **Reconnect** feature located on the **[Net/Shape]** tab. This function will simply optimize the appearance of the connections thus eliminating length. This does not have any impact on the Signal integrity constraints.

Note: PCB design shown after reconnect function has been run.

Note: the reuse block has been moved slightly by the author from its original location for image clarity.

If you have not completed the design to this point, please load **Rainmaker5\_CS.PCB**, save it as **Rainmaker5.pcb**.

Next we can move the reuse circuit block into position. Since the block is grouped. It is possible to click on it and move it as a single object. It may also be rotated on any angle.

Even though the amplifier reuse block does not quite fit. This is OK and probably a normal occurrence for the experienced PCB designer. Later we will remove the reuse block association make some placement adjustments and *copper pour* template adjustments. The point of the exercise is basic Design Reuse techniques.

5. Place the block as shown below.

**Tip**: if you pick an object by a location that you would like to change while in the "Move" mode, click the <**R.M.B**.> and select the "**Change Selection Origin**". This will temporarily suspend the movement while you select a different location. Once you click the object the movement will resume.

**Tip:** Enable the Snap point function located on the [**Design**] tab before changing a selection origin.

6. Place the Starpoint **STP1**, relay **RL1** and the **SP1** and **SP2** components in the suggested approximate locations shown on the next page. **Fix** them once they are placed by selecting them and clicking **<R.M.B.>** and clicking on the **Fix** function.

- 7. Select the **Embedded Place and Route** icon located on the [Tools] tab.

- 8. Arrange the components around the board outline using the **Stack** function located on the **[Home]** tab.

- Select the Move icon and the Component mode focus icon and manually place the other components.

10. Exit the Embedded Place and Route and save the PCB Design.

#### Adjusting the Reuse Circuit block.

At this point we will make the necessary adjustments to the circuit block so that it fits with this board outline.

- Select the Amplifier reuse block. From the non-modal Item properties panel, turn off the Grouped setting.

- 12. Start by modifying the shapes of the existing copper pour templates that are a part of the reuse block. They can be selected and stretched to the left of the board outline as shown in the image. →

- 13. Delete the round cut-outs that in the templates. There are 8 total, 4 on each template.

14. Open the **Current Design** panel on the left side of the application window. Expand the Reuse Block branch, click on the Amplifier name and click the **<R.M.B.>**. Select **Remove Reuse Association**. You are now free to make any edits to the circuit block you wish.

**Note:** This is an optional process, it is not necessary to remove the association. If a PCB design warrants this technique, it is recommended to also remove the reuse association in the schematic reuse block as well.

However if you pay attention to the intricacies of the block and later **remote select** the PCB block items from the Schematic window using Cross probing, you can create a new reuse block of the same name to insure that it remains in synch with the schematic.

- 15. Select the copper polygons and associated templates and delete them from both Top and Bottom layers.

- 16. Select the **Embedded Place and Route** icon located on the [Tools] tab.

- 17. Use the move commands in the **Component** focus mode to adjust the placement of the two capacitors and perhaps **R1005** to a more proper location.

If you encounter any errors that you wish to ignore, click the <R.M.B.> and select Toggle errors allowed.

As you move routed components, the routes should remain routed as they move with them. .

18. Exit the Embedded Place and Route and save the PCB Design.

Sample of finished Placement

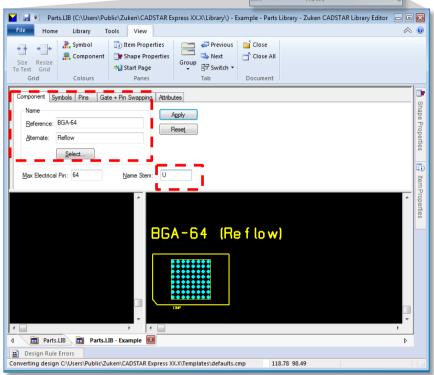

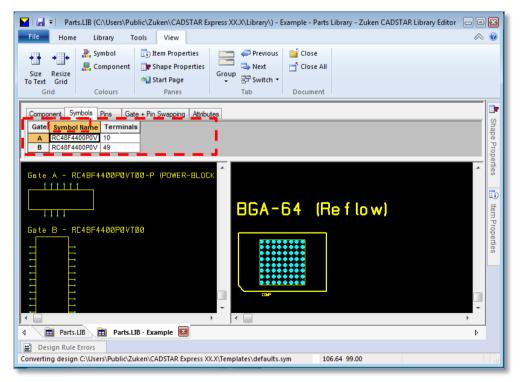

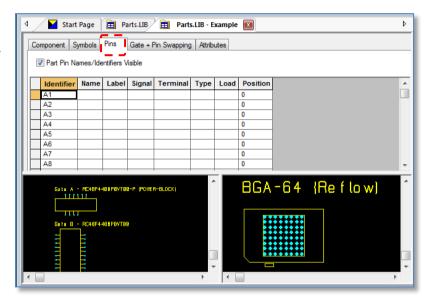

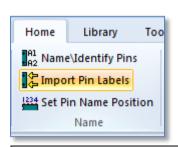

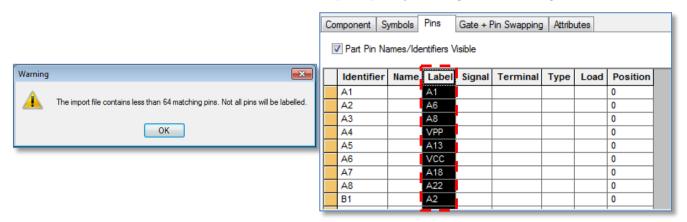

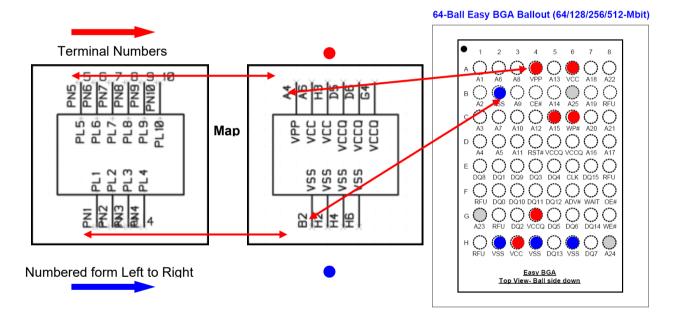

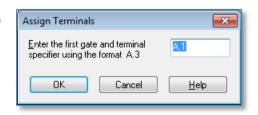

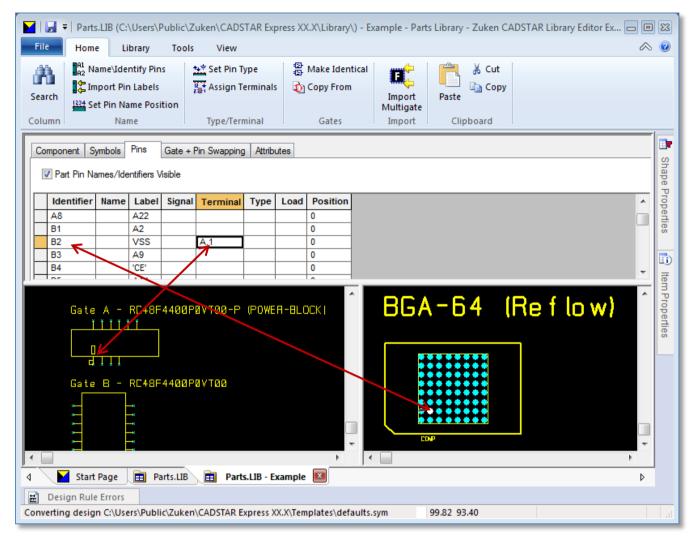

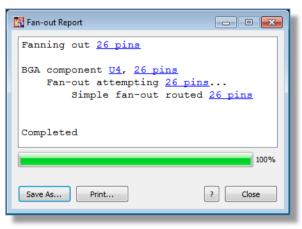

If you didn't manage to place the components, just open **Rainmaker6\_CS.PCB** and save it as **Rainmaker6.pcb**. This file has the copper and templates already removed.