# CADSTAR FPGA

# Complete FPGA-PCB Design Flow Tutorial

created by:

# Table of Contents

| Introduction                                                            | 2  |

|-------------------------------------------------------------------------|----|

| Creating a New Design                                                   | 2  |

| Choosing Workspace and Design Names                                     | 2  |

| Creating First Design Files                                             | 5  |

| Creating Top-Level                                                      | 12 |

| Compiling and Simulating                                                | 14 |

| Basic Debugging                                                         | 17 |

| Using Existing design for FPGA-PCB design flow                          | 17 |

| Synthesis with Xilinx ISE/WebPack 9.2 XST VHDL/Verilog                  | 20 |

| Post-Synthesis Simulation                                               | 24 |

| Generating I/O Pin Constraints File for Implementation                  | 25 |

| Implementation with Xilinx ISE and Providing Implementation Constraints | 28 |

| Implementation with Xilinx ISE/WebPack in GUI Mode                      | 31 |

| Timing Simulation                                                       | 33 |

| Export of Implementation Reports Constraints file to CADSTAR PCB Tool   | 35 |

| CADSTAR Schematics Block Creation                                       | 33 |

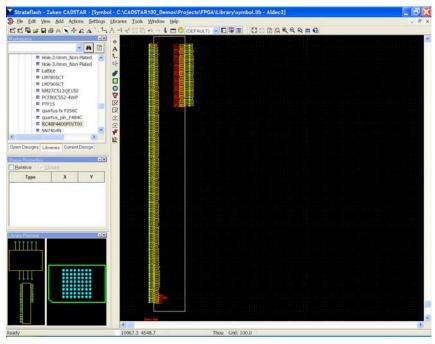

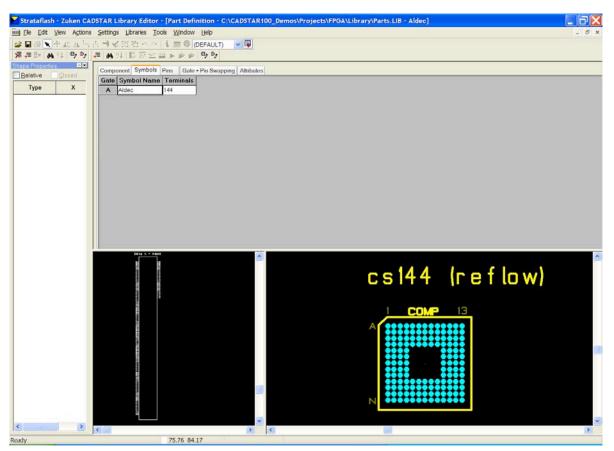

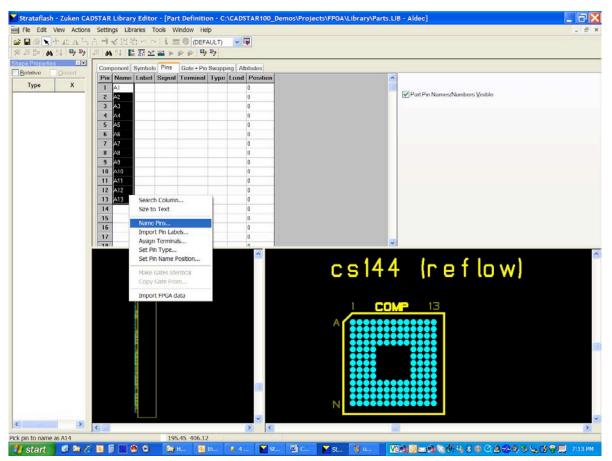

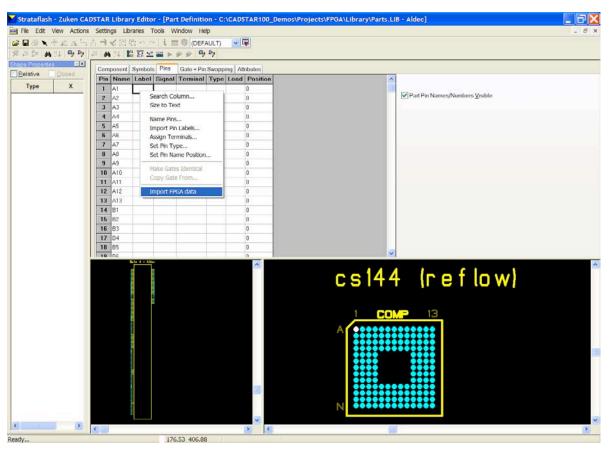

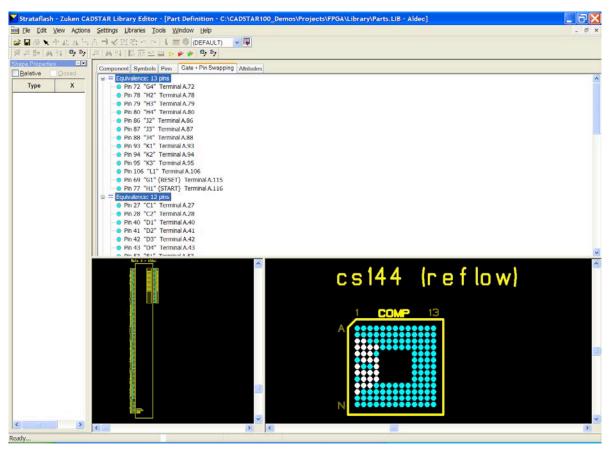

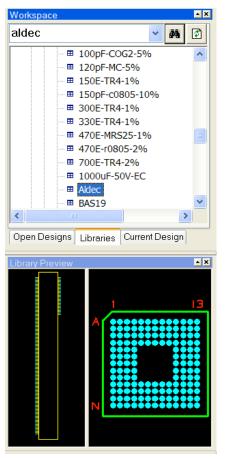

| CADSTAR Parts Library Editor                                            | 37 |

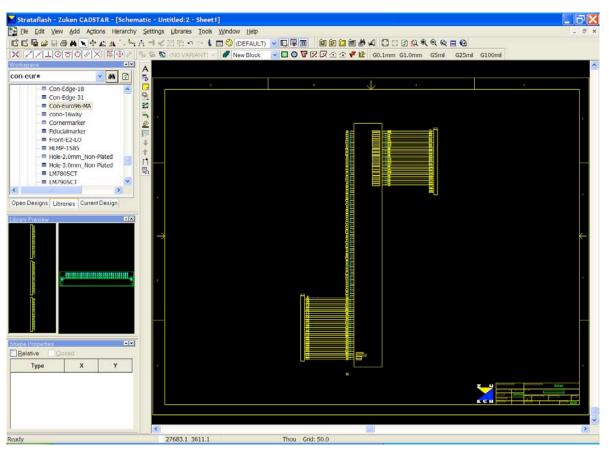

| CADSTAR Schematic Design                                                | 45 |

| CADSTAR PCB Design                                                      | 48 |

| CADSTAR P.R. Editor XR (Place and Route Editor)                         | 51 |

| Import of SWAP Pin file from CADSTAR to Active-HDL                      | 53 |

| Conclusion                                                              | 60 |

#### Introduction

This Tutorial was created to help you become familiar with the basic features of Active-HDL CADSTAR edition lite in the shortest possible time. No prior knowledge of HDL simulation tools is required, but elementary knowledge of VHDL will be helpful.

If you want to refresh your VHDL, you are welcome to use our Interactive VHDL Tutorial: just go to the *Help* menu, and then select the *Interactive VHDL Tutorial* option. The same tutorial is also accessible directly from the installation CD.

While reading this Guide, you will be able to create, compile, simulate and debug a simple, but fully functional design of a Counter. First section of the tutorial will use Xilinx ISE/WebPack 9.2 XST VHDL/Verilog and Xilinx ISE/WebPack 9.2 as Synthesis and Implementation tools respectively.

During the installation of Active-HDL CADSTAR edition lite, user has the option to choose and install pre-compiled ready to use FPGA vendor libraries inside Active-HDL. It is highly recommended that the user installs the FPGA vendor libraries that he will need to use in his design. There is also an option to update to the latest version of FPGA vendor libraries from within Active-HDL CADSTAR Edition Lite by choosing Help-> Aldec on the Web ->Download Active-HDL Updates. If user does not install the vendor libraries during Active-HDL installation, then he has to bring the vendor libraries and recompile them inside Active-HDL.

The application note <u>http://support.aldec.com/KnowledgeBase/Article.aspx?aid=00003</u>3 describes the steps needed to recompile the libraries.

**Note**:[For the purpose of this tutorial **Xilinx ISE Webpack** Synthesis and Implementation tools will be used. They are free tools from Xilinx and can be downloaded from

<u>http://www.xilinx.com/ise/logic\_design\_prod/webpack.htm</u> Similarily, free vendor tools from Altera, Actel, Lattice and Quicklogic can also be downloaded from their respective websites and can be set up in Active-HDL the same way as Xilinx ISE Webpack.]

The first section of the Guide covers VHDL and Verilog entry, utilization of Language Assistant utility of Active-HDL while creating your design, interactive simulation and standard debugging. The second section emphasizes on using existing sample design for Synthesis, Implementation, I/O FPGA Pin assignment and export and import of I/O pin files to and from CADSTAR PCB tool.

#### Creating a New Design

#### Starting from the Opening Screen

If you double-click the Active-HDL icon on your desktop, you should see the splash-screen for a while, then the *Getting Started* window with the Active-HDL GUI in the background.

Right in the middle of that window you should notice a *Create new workspace* radio button. Select this button, and then click *OK*.

#### Starting from the GUI

If Active-HDL is already open (e.g. you were playing with sample designs) go to the *File* menu, select *New*, then *Workspace*.

#### **Choosing Workspace and Design Names**

No matter if you started from the GUI or the Getting Started window, you should see a *New Workspace* window. Type the name of the workspace (*MY\_WORKSPACE*) in the first field; keep the *Add New Design to Workspace* checkbox selected and click *OK*.

2. The **New Design Wizard** window appears. In this new window, select **create an empty design** with design flow and click next>.

| lew | Design Wizard                                                                                                                                                                                                                                 | × |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|     | How would you like to create Design Resources?                                                                                                                                                                                                |   |

|     | C Create an Empty Design                                                                                                                                                                                                                      |   |

|     | Create an Empty Design with Design Flow                                                                                                                                                                                                       |   |

|     | C Add existing Resource Files                                                                                                                                                                                                                 |   |

|     | Import a Design from Active-CAD                                                                                                                                                                                                               |   |

|     | This option creates an empty design and enables Design<br>Flow Manager. You can select a vendor of your synthesis or<br>implementation tool, technology, libraries, and specify the<br>default HDL language of your new design entry sources. |   |

|     | C Create New Workspace                                                                                                                                                                                                                        |   |

|     | Add Design to Current Workspace                                                                                                                                                                                                               |   |

|     | < Back Next > Cancel                                                                                                                                                                                                                          |   |

Figure 1: New Design Wizard.

Click on the *Flow Setting* tab in the new window. Click on the *select* tab of the HDL synthesis tool and select the Xilinx ISE/WebPack 9.2 XST VHDL/Verilog from the option. Now click on the *select* tab of the implementation tool. Select Xilinx ISE/WebPack 9.2 from the option. Now scroll down the window saying *family* and select *virtex*. Click OK.

You can also select your choice [for example Precision RTL] of synthesis tools and implementation tool [for example Actel Designer] in the flow setting window the same way as Xilinx ISE/ Webpack 9.2

| Flow Configuration Settings                                                                                                       |        |

|-----------------------------------------------------------------------------------------------------------------------------------|--------|

| C Synthesis:<br>Tool name: <none></none>                                                                                          | Select |

| HDL Synthesis:<br>Tool name: Xilinx ISE/WebPack 9.2XST VHDL/Verilog Use Server Farm NONE                                          | Select |

| Physical Synthesis:<br>Tool name: <a href="https://www.none-internationalistics.com">https://www.none-internationalistics.com</a> | Select |

| Implementation:<br>Tool name: Xilinx ISE/WebPack 9.2<br>Use Server Farm NONE                                                      | Select |

| Simulation: Use Server Farm NONE  Family: Xilinx9x VIRTEX                                                                         | -      |

|                                                                                                                                   | Help   |

**Figure 2: Flow Settings**

- 4. Now you are back to the same window again but with enabled flow setting. Click next now.

- 5. Type the name of the design *Counter* in the new window and click next and click finish.

- 6. Now what you see in the design flow manager area is a complete FPGA flow starting from design entry to timing simulation. In addition you will see option for PCB Interface for Pin file Export/Import to and from CADSTAR PCB tool.

Your new workspace and design are ready to use!

To learn more about workspaces and designs, go to *Active-HDL On-line Documentation*, then in the Contents tab select *Active-HDL Help / Using Active-HDL / Workspaces and Designs*.

#### **Creating First Design Files**

#### Creating Cnt\_4b.Vhd

The first source file we are going to create describes a Counter. The interface of the Counter can be quickly created using the *New Source File Wizard* and *Language Assistant*

- 1. From the main menu, Go to File->New ->VHDL Source. Click "Next" in the New Source File Wizard.

- 2. Type cnt\_4b as the name of source file in the first box as shown in the Figure 3 . Click Next.

| New Source File Wiza | ırd - Name 🛛 🔀                                            |

|----------------------|-----------------------------------------------------------|

|                      | Type the name of the source file to create:               |

|                      | cnt_4b Browse                                             |

|                      | You can use the Browse button to specify the file.        |

|                      | Type the name of the entity (optional):                   |

|                      |                                                           |

|                      | By default, the entity name is the same as the file name. |

|                      | Type the name of the architecture body (optional):        |

|                      | By default, the architecture name is the same as the      |

|                      | entity name.                                              |

|                      |                                                           |

|                      | < <u>B</u> ack ( <u>Next</u> > Cancel                     |

Figure 3: New Source File Wizard

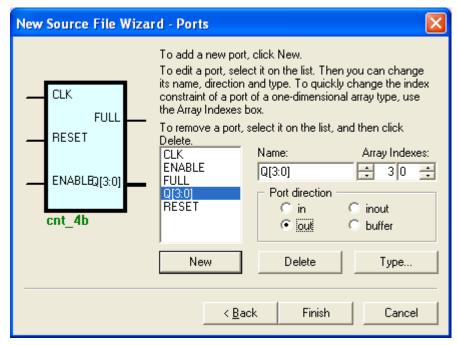

3. In the next window, you will add ports to your source file. Click on "New" and type "CLK" under the "Name" tab. Make sure the Port direction is "in" as shown in Figure 4.

| New Source File Wi | zard - Ports                                                                                                                                                                                                                     |         |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                    | To add a new port, click New.<br>To edit a port, select it on the list. Then you can ch<br>its name, direction and type. To quickly change the<br>constraint of a port of a one-dimensional array type<br>the Array Indexes box. | e index |

| CLK                | To remove a port, select it on the list, and then clic<br>Delete.<br>CLK Name: Array Ir<br>CLK                                                                                                                                   |         |

| cnt_4b             | Port direction                                                                                                                                                                                                                   |         |

|                    | New Delete Typ                                                                                                                                                                                                                   | ie      |

|                    | < <u>B</u> ack Finish Ca                                                                                                                                                                                                         | incel   |

Figure 4: Ports

4. Click on the "New" tab again and declare "RESET" with Port direction as "in". Similarly declare "ENABLE" as "in", FULL as "out". Finally declare "Q" as "out" and type "3" in first column of "Array Indexes" so that width of output port Q is 4-bit. Once you declare the ports the "New Source File Wizard" should look like in Figure 5. Click Finish.

Figure 5: Ports

You will see cnt\_4b.vhd in your design in the Design Browser. And it is almost ready except for the architecture body. You can make use of "Langauge Assistant" to fill the body of the architecture.

With the cursor placed in the body of the archictecture, click on the icon  $\Im$  for Language Assistant in the tool bar above. You can also select "Language Assistant" by going to Tools-> Language Assistant option from the main menu.

With the HDL Language selected as VHDL, Expand the "Tutorial" and click in "Counter" to find readily available process for our Counter, cnt\_4b.vhd. Click on Use template icon and the process will be automatically inserted in the body of the architecture of cnt\_4b.vhd.

| 🗣 Language Assistant                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VHDL 💽 🎦 🖆 🖬 🗙 🗌                                                                                                                                                                                                   | × 🖻 🗘 🐇                                                                                                                                                                                                                                                                                                                                                                          |

| Templates Code Auto Complete Auto Complete Auto Complete Auto Completes Auto Completes Auto Completes Simulation templates Synthesis templates Training Counter Decoder Top Top_2 User templates Utility templates | <pre>Use template process (ULK, RESET) variable Qint: STD_LOGIC_VECTOR (3 downto 0); begin     if RESET='1' then         Qint := "0000";     else         if CLK'event and CLK='1' then             if Qint&lt;9 then             Qint:=Qint+1;         else             Qint:="0000";         end if;         end if;         end if;         q &lt;= Qint; end process; </pre> |

| Inserts template into the document                                                                                                                                                                                 | NUM INS //                                                                                                                                                                                                                                                                                                                                                                       |

Figure 6: Language Assistant

To learn more about the Language Assistant, go to Active-HDL On-line Documentation, then in the Contents tab select Active-HDL Help / Active-HDL Tools / Language Assistant.

The cnt\_4b.vhd is almost ready. Declare the ieee library clause for unsigned arithmetic,

$use \ \textbf{IEEE.STD\_LOGIC\_UNSIGNED.all;} in the \ \textbf{Library declaration part at the top}.$

The source code for cnt\_4b will look like as shown in Figure 7

```

24

25

library IEEE;

use IEEE.STD LOGIC 1164.all;

26

use IEEE.STD LOGIC UNSIGNED.all;

27

28

29

entity cnt_4b is

30

port(

31

CLK : in STD LOGIC;

RESET : in STD LOGIC;

32

33

ENABLE : in STD LOGIC;

34

FULL : out STD LOGIC;

35

Q : out STD_LOGIC_VECTOR(3 downto 0)

36

);

37

end cnt 4b;

38

39

--}} End of automatically maintained section

40

41

architecture cnt_4b of cnt_4b is

42

begin

43

44

45

process (CLK, RESET)

46

variable Qint: STD LOGIC VECTOR (3 downto 0);

47

begin

48

if RESET='1' then

49

Qint := "0000";

50

else

51

if CLK'event and CLK='1' then

52

if Qint<9 then

53

Qint:=Qint+1;

54

else

55

Qint:="00000";

56

end if;

57

end if:

58

end if:

59

Q <= Qint;

60

end process; -- enter your statements here --

61

62

end cnt 4b;

<u>___</u>

```

Figure 7: cnt\_4b.vhd

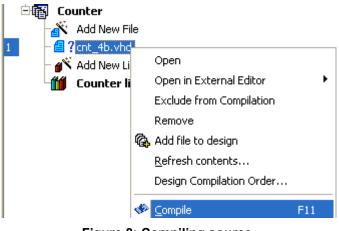

Compile source file created at the end of wizard to check any possible DRC error as shown in Figure 8.

Figure 8: Compiling source.

# Creating and 2.v

- 1. From the main menu, Go to File->New ->Verilog Source. Click "Next" in the New Source File Wizard.

- 2. Type and 2 as the name of source file and Click Next.

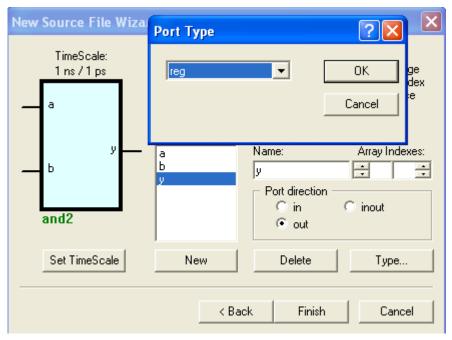

- 3. In the next window, you will add ports to your source file just like before. Have two input ports by name "a" and "b". Add an output port by name "y". For output "y" click on "Type" tab and select the Port Type as "reg" as shown in Figure 9. Click OK and Click Finish.

Figure 9: Ports and Port Type

4. In the generated and2.v, please insert following statements just before the statement endmodule. always @ (a or b)

y <= a & b;

The and2.v should look like as shown in Figure 10.

www.cadstarworld.com

```

//-----

`timescale 1 ns / 1 ps

//{{ Section below this comment is automatically maintained

and may be overwritten

11

//{module {and2}}

module and2 ( y ,a ,b );

output y ;

reg y ;

input a ;

wire a ;

input b ;

wire b ;

//}} End of automatically maintained section

// -- Enter your statements here -- //

always 0 (a or b)

y <= a & b;

endmodule

```

#### Figure 10: and2.v

5. Compile source file created just like before to check any possible DRC error.

Now we will create the top-level for our design using Block Diagram Editor.

#### **Creating Top-Level**

- 1. To get back to the design flow manager, press [ALT+3] on the keyboard.

- 2. Click the **BDE** tab to start the Block Diagram Editor.

- 3. Mark the option Add the generated files to the design. And Click on the next.

- 4. In the window select the language as Verilog and click on the next.

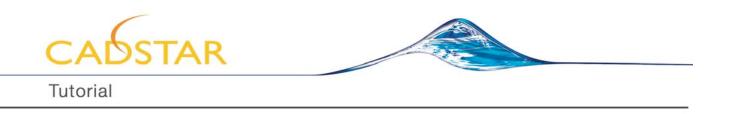

- 5. Type the name of the source file as *CNT\_BCD* and click on the *next*.

- 6. In the next window click on the tab *NEW*, type *CLK* in the *NAME* window, select port direction as *IN* and hit enter on the keyboard. Add *RESET* and *GATE* following the same method.

- 7. Add *FULL* as an output. Also add *BCD\_A,BCD\_B,BCD\_C,BCD\_D* as outputs with array index defined as 3:0.

- 8. Click finish and end Block Diagram Wizard, it opens the Block Diagram Editor file on the screen with all your inputs and outputs defined in it.

- 9. Now hit [**s**] on the keyboard or click on <sup>D</sup> icon to open the symbol toolbox.

10. Drag and drop and2, cnt\_4b symbols to your diagram editor so that the diagram contains three instances of and2 and four instances of cnt\_4b symbols on the diagram.

| Symbols Toolbox                           | * X        |

|-------------------------------------------|------------|

|                                           |            |

| Name 🛆                                    | Descriptic |

| 🗄 Built-in symbols                        |            |

| 🗆 Counter                                 |            |

| and2                                      |            |

| cnt_4b                                    |            |

| <ul> <li>Units without symbols</li> </ul> |            |

|                                           |            |

| → <mark>CLK FULL</mark>                   | ⊢          |

| + ENABLE Q(3:0)                           | -          |

| + RESET                                   |            |

|                                           |            |

Figure 11: Symbol Toolbox.

11. Click on  $\bigcirc$  icon and drag and drop the Global wire on to Diagram. Drop it two times as we need two Global wires one for CLK and one for RESET. Hit "Esc" On Keyboard.

12. Now double click on the  $\bigcirc$  icons in Diagram and give the net name as CLK and RESET respectively.

12. Use shortcut [w] for wire and [b] for bus to connect different ports to respective location. [See Figure 12]

Figure 12: Block Diagram Editor Connections

To learn more about the Block Diagram Editor, go to *Active-HDL On-line Documentation*, then in the Contents tab select *Active-HDL Help / Active-HDL Tools / Block Diagram Editor*.

# **Compiling and Simulating**

To compile the source file in Active-HDL you have several options:

- Right-click the icon of the source file in the Design Browser and select **Compile** from the popup menu.

- While the source file is open for editing/viewing, click the *Compile* button (\*) on the main toolbar.

- While the source file icon is selected or the file is open, hit the *F11* key on your keyboard.

When compiling or simulating Verilog modules, Do not forget to add Verilog libraries to Design settings window. Go to **Design>>Settings** and add required libraries to subcategory **Verilog** of **compilation** and **simulation**.

Using the method you prefer, compile the CNT\_BCD.bde file.

If the compilation was successful, a green confirmation message will be displayed in the **Console** window at the bottom of the workspace. If you see red messages in the console, it means that some errors were detected. In that case you should read the error message carefully, double-click the text of the message in the console to highlight the offending line in the source code (the document will be opened if it wasn't), correct the mistake and save/compile again.

A successfully compiled source file icon will have the list of the design units detected inside the file during compilation. Click the plus sign to the left of the CNT\_BCD.bde icon to display the green [M] icon for the *module* detected while compiling the file.

Before you start the simulation, some module must be selected as the top level of your design. Since PulseGen is our design is being built as **top-level**, right click on the module icon of the **PulseGen** and click on the **Set as Top-Level**. When there are multiple pairs in your design, you can select one of them from the drop-down list at the very top of the Design Browser window.

| Design Browser      | × ×                                       |

|---------------------|-------------------------------------------|

| Top-Level selection | •                                         |

| O Unsorted          |                                           |

| 🛛 🗗 🔐 Workspace 'MY | _WORKSPACE': 1 design(s)                  |

| 🗆 🗃 Counter         |                                           |

| Add New File        |                                           |

| 1 🕀 🔠 🗸 cnt_4b.vhd  |                                           |

| 2 ⊞ 🛃 √and2.v       |                                           |

| 3 ⊡⊅√CNT_BCD.bde    |                                           |

|                     |                                           |

| - 🔏 Add New Libra   |                                           |

|                     |                                           |

|                     | Generate TestBench                        |

|                     | 📣 Generate Block Description for Simulink |

|                     | Edit Symbol                               |

|                     |                                           |

|                     | Copy SystemC Class Declaration            |

|                     | Copy VHDL Instantiation                   |

|                     | Copy Verilog Instantiation                |

Figure 13: Setting Top-Level from Design Browser

When *CNT\_BCD* is selected as the top level, you can start your simulation.

- 1. Select *Simulation* | *Initialize Simulation* from the menu; wait till the design browser switches to the *Structure* tab automatically.

- 2. Select File | New | Waveform from the menu (or click the matching icon in the main toolbar).

- 3. Highlight the green chip icon for *CNT\_BCD* from the **Structure** tab of Design Browser window. The bottom window of Structure tab displays the signals. Using CTRL keystroke, select the signals *CLK*, *RESET*, *GATE*, *BCD\_A* and drag and drop them onto the waveform editor.

- 4. We will Right-click the *CLK* port name in the waveform window and select *Stimulators* from the pop-up menu.

- 5. Drag the floating *Stimulators* window (Figure 14) to the bottom of the screen, so that you can see both the window and all signals in the waveform.

| M Stimulators                        |                                   | ? 🛛                                                         |

|--------------------------------------|-----------------------------------|-------------------------------------------------------------|

| Signals Hotkeys Predefined           |                                   |                                                             |

| Signals:<br>Name Type<br>✓ CLK Clock | Type:<br>Clock<br>f(t)<br>Formula | Forces a clock pulse of a specific frequency and duty cycle |

| Display paths Save                   | 010<br>110<br>Valu 🗸              | Apply Strength: Override  Close                             |

Figure 14: Stimulators window with Clock stimulator type selected.

- While *CLK* is highlighted in the *Signals:* list, select *Clock* as the stimulator in the *Type:* list. Adjust clock frequency to 100MHz (clock period will adjust automatically to 10 ns) the *Stimulators* window should look exactly as in Figure 10. Click *Apply*.

- 7. Without closing the *Stimulators* window, click the *RESET* port name in the waveform; the port name should be transferred to the *Signals:* list in the Stimulators window.

- Select *Formula* as the stimulator type for *RESET* and type 1 0 ns, 0 120 ns in the *Enter formula* field (don't skip any spaces!). Click *Apply*.

- 9. Without closing the *Stimulators* window, click the *GATE* port name in the waveform. Select *Formula* as the stimulator type for *GATE* and type

0 0ns, 1 220 ns

- 10. Click *Apply* and close the *Stimulators* window.

- 11. Select Simulation | Run Until... from the menu. Type 500 ns in the Run Until window. Click OK.

| Name      | Value | Sti | 1 · 20 · 1 · 40 · 1 · 60 · 1 80 · 1 100 · 120 · 140 · 160 · 180 · 200 · 220 · 240 · 260 · 280 · 300                      |

|-----------|-------|-----|--------------------------------------------------------------------------------------------------------------------------|

| ► CLK     | 1     | Clo |                                                                                                                          |

| ► GATE    | 1     | For |                                                                                                                          |

| ► RESET   | 0     | For |                                                                                                                          |

| . ● BCD_A | 0     |     | (8, 7, 8, 2, 2, 2, 2, 2, 9, 8, 7, 3, 3, 4, 2, 2, 1, 2, 2, 1, 2, 2, 1, 2, 2, 2, 1, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, |

Figure 15: Functional Simulation Output

Analyze the results displayed in the waveform. If you are curious what is the signal value represented by a section of the waveform, click it and examine the *Value* field right by the signal name.

When you are done, select *Simulation* | *End simulation* from the menu, save the waveform as CNT\_BCD.AWF and close the waveform window.

To learn more about simulation, go to *Active-HDL On-line Documentation*, then in the Contents tab select *Active-HDL Help / Using Active-HDL / Simulation*. We will be conducting more simulations in this guide.

#### **Basic Debugging**

Simulate the top level again. This time do not end simulation – use **Restart** toolbar button (or **Simulation** | **Restart Simulation** option from the main menu) to return to simulation time 0.

- 1. Run simulation for 10 us.

- Use *Trace Into* button in the toolbar or F7 key to step through the execution of your code. Observe yellow highlight marking currently executed line of your HDL code. Notice current values of signals displayed inside rectangular probes visible on block diagrams. (You can open sources manually or wait until they are executed and displayed automatically.)

- 3. Open any source file and find the line where you want the simulation to stop. Click that line and hit **F9** on your keyboard to set breakpoint.

- 4. Use *Run* button in the toolbar or Alt+F5 keys on your keyboard to run simulation. Observe how simulation stops at the breakpoint. You can see the time when simulation stopped in the console or in the special field at the end of the toolbar.

- 5. End simulation and clear breakpoints (*Simulation* | *Clear All Breakpoints* option from the menu).

To learn more about debugging, go to *Active-HDL On-line Documentation*, then in the Contents tab select *Active-HDL Help / Using Active-HDL / Debugging HDL Code*.

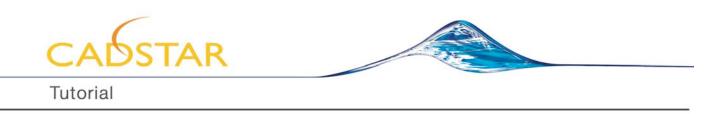

#### Using Existing design for FPGA-PCB design flow

Now that we have learnt how to create a workspace with a mixed language design, simulation and debugging, let's use an existing sample design and go through Synthesis, Implementation, specifying FPGA Pin Constraints and export/import of pin information file to and from PCB tool CADSTAR.

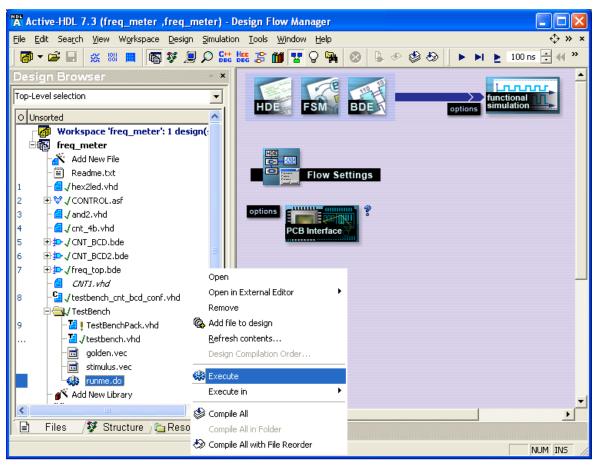

We will use the sample design that comes with the installation of Active-HDL. From the main menu, go to File->Open Workspace/Design Explorer. In the Workspace/Design Explorer window, select Active-HDL->Samples->VHDL\_designs->freq\_meter. Double click on the freq\_meter. freq\_meter workspace with the design freq\_meter attached appears inside Active-HDL as shown in Figure 16.

Figure 16: Sample Design freq\_meter

If you examine the design, it contains mixture of HDL files, graphical Block Diagram Editor files and State Diagram Editor file. Expand the "TestBench" folder and execute the runme.do file as shown in Figure 17.

Figure 17: Execute runme.do

The runme.do contains commands that compiles all the design files and simulates the testbench. The results of functional simulation are shown in Figure 18.

| Name                 | Value | Sti | 13 13,5 14 14,5 15 15,5 16 16,5 17 17,5 18 18,5 19 19,5 . 20 . |

|----------------------|-------|-----|----------------------------------------------------------------|

| ■ STIM_F_INPUT       | 1     |     |                                                                |

| ■ STIM_F_PATTE       | 0     |     |                                                                |

| ■ STIM_RESET         | 0     |     |                                                                |

| ■ STIM_START         | 1     |     |                                                                |

| ■      ■ EXPECTED_LE | 40    |     |                                                                |

| ■      ■ EXPECTED_LE | 40    |     |                                                                |

| ■      ■ EXPECTED_LE | 78    |     | <u>)                                    </u>                   |

|                      | 78    |     |                                                                |

| ■ M ACTUAL_LED_A     | 40    |     |                                                                |

|                      | 40    |     |                                                                |

| ■ ACTUAL_LED_C       | 78    |     | <u> </u>                                                       |

| ■ ▲ ACTUAL_LED_D     | 78    |     |                                                                |

Figure 18: Functional Simulation

When the simulation finishes, click on "OK" in "Simulation" Dialog box and save the waveform by choosing File->Save as from the main menu. You can save the waveform as "functional.awf".

Now click on the "Flow Settings" to set the HDL Synthesis tool and Implementation tool for this design. We will again use **Xilinx ISE/WebPack 9.2 XST VHDL/Verilog** as HDL Synthesis tool and **Xilinx ISE/WebPack 9.2** as implementation tool.

#### Synthesis with Xilinx ISE/WebPack 9.2 XST VHDL/Verilog

After RTL simulation has been completed in Active-HDL, the files can be passed to Synthesis. Synthesis settings can be configured with the Synthesis **options** button in the Design Flow Manager.

1. Clicking on the Synthesis **options** [ synthesis.

button invokes the options window for

2. Make sure all design files are on the design tree of the synthesis option. You can select or deselect them by right clicking them. Let's have six design files selected for Synthesis as shown in Figure 19.

| Synthesis Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Design Files:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                               |

| ⊕ 🗃 aurora.adf<br>⊕ 🗃 bjack.adf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | /General / Std Synthesis / Adv Synthesis / HDL 1 / HDL 2 / Xilinx Specific / Include Dirs / Libraries / Servei K S<br>Top-level Unit freq top |

| terational data and terat | Family Xiinx9x VIRTEX  Device v50cs144                                                                                                        |

| Freq_meter.adf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Speed Grade -6                                                                                                                                |

| 1 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Simulation Output Format: C None C VHDL C Verilog           Filter Messages         Browse                                                    |

| 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Generate Synth. Script                                                                                                                        |

| € IIInx_MGT.adf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | [OK]Help                                                                                                                                      |

Figure 19: Xilinx ISE/WebPack XST Synthesis Options

3. Select Top-Level, Family, Device and speed grade as freq\_top, virtex, v50cs144 and 6 respectively as shown in Figure 20.

| Top-level Unit | freq_top          |        | ~          |  |

|----------------|-------------------|--------|------------|--|

| Family         | Xilinx9x VIRTEX 😽 | Device | v50cs144 🗸 |  |

| Speed Grade    | -6 💌              |        |            |  |

Figure 20: Selecting Top-Level, family and device.

- 4. Select simulation output format to VHDL

- 5. You can select and set other synthesis options also from the window.

- 6. When you are done with all the settings you can click on OK.

- 7. Now you can automatically perform push-button Synthesis by clicking the synthesis

|             | <u> </u>                  |          |

|-------------|---------------------------|----------|

|             | $\supset \mathcal{H}_{-}$ |          |

|             | = -                       | <b>h</b> |

|             | and the second            |          |

| S١          | /nthesis                  |          |

| <b>1</b> 22 | 10010                     |          |

button in the Design Flow Manager.

8.

If synthesis is run in **batch mode**, Active-HDL takes full control of the process. All files will be automatically passed to the Synthesis tool and when Synthesis is complete; all results from the Synthesis Tool will be passed to Active-HDL. If the Synthesis tool is run in **GUI mode (This option is available for Select Synthesis tools in Active-HDL)**, then Active-HDL passes all the necessary design files to the Synthesis tool and the resulting files after synthesis can be back annotated into Active-HDL in a semi-automatic way.

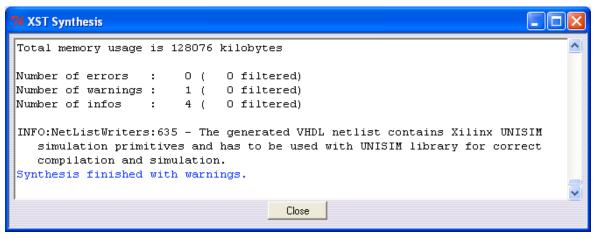

**9.** While the Synthesis is running, all of the Synthesis results and information can be seen on-line in a special window.

Figure 21: Xilinx XST Synthesis window.

**ZUKEN**

21

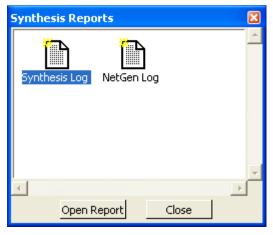

10. Synthesis reports can then be viewed by clicking on the corresponding Synthesis **reports** button in the Design Flow Manager.

Figure 22: Synthesis Reports Window

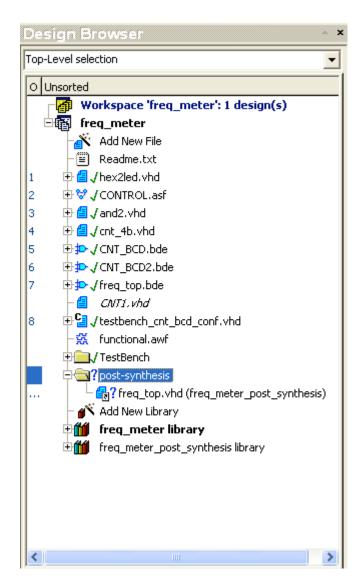

11. You will see new folder and new libraries named post-synthesis created in the Design Browser.

Figure 23: Design Browser after Post-Synthesis.

23

# **Post-Synthesis Simulation**

1. Click on the *options* tab of the post synthesis simulation icon.

Figure 24: Post-Synthesis simulation tab

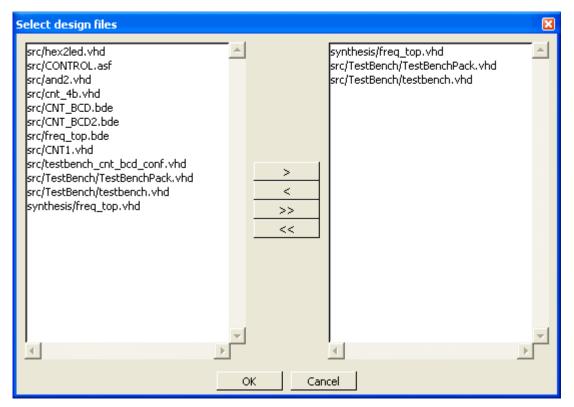

Click on the icon to add synthesis netlist (synthesis/freq\_top.vhd) and testbench file src/TestBench/TestBenchPack.vhd, src/TestBench/testbench.vhd in that order to opened window. Click **OK** when you are done adding files.

Figure 25: Selecting netlist file and testbench files for simulation.

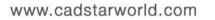

3. Now click on the *choose* button to select the top-level of your design. Select "testbench", Click "Add" and click OK to go back to the options window again.

| Select top | level unit | (s) |        |   | X        |

|------------|------------|-----|--------|---|----------|

| Top-level: | testbench  |     |        |   | Add      |

| testbench  |            |     |        |   | *        |

|            |            |     |        | 1 | <b>v</b> |

|            |            | OK  | Cancel |   |          |

Figure 26: Selecting top-level of the design.

4. Click on the *post-synthesis tab* and wait till waveform editor window opens. Once waveform editor window opens, click on *run for* 25 us tab. Check for any mismatches in the waveform.

| Name                 | Value           | Sti | 14,5 + + 15 + + 15,5 + + 16 + + 16,5 + + 17 + + + 17,5 + + 18 + + + 18,5 + + 19 + + + 18,5 + + 20 + + |

|----------------------|-----------------|-----|-------------------------------------------------------------------------------------------------------|

| ■ # ACTUAL_LED_A     | 40              |     |                                                                                                       |

| ■ ■ ACTUAL_LED_B     | 40              |     |                                                                                                       |

| ■ # ACTUAL_LED_C     | 12              |     | <u> </u>                                                                                              |

| ■ # ACTUAL_LED_D     | 02              |     |                                                                                                       |

| ₩ END_SIM            | false           |     |                                                                                                       |

|                      | 40              |     |                                                                                                       |

|                      | 40              |     |                                                                                                       |

|                      | 12              |     | <u></u>                                                                                               |

| ■      ■ EXPECTED_LE | 02              |     |                                                                                                       |

| 🛨 🌌 PATTERN          | (40,40,12,02    |     |                                                                                                       |

| ■ STIM_F_INPUT       | 0               | 1   |                                                                                                       |

| ■ STIM_F_PATTE       | 0               | 1   |                                                                                                       |

| ■ STIM_RESET         | 0               |     |                                                                                                       |

| STIM_START           | 1               |     |                                                                                                       |

|                      | (0,0,0,1,false) |     |                                                                                                       |

Figure 27: Post-synthesis Simulation Output.

#### Generating I/O Pin Constraints File for Implementation

Now we are ready to implement our design to Xilinx Virtex FPGA. Before we start the implementation process, a very important step is to define the I/O Pin Constraints for the design. To write the Constraints file we can use the Xilinx PACE and Constraints Editors.Click on the Tools button

in the design flow manager. "Tools" button opens up Design Entry tools of Xilinx and it includes PACE and Constraints Editor tools.

Figure 28: Xilinx Design Entry Tools

Pinout and Area Constraints Editor (PACE) is an interactive graphical tool that you can use to:

- 1) View and edit location of constraints for I/Os and global logic

- 2) View and create area constraints for logic in the design

- 3) Determine resource requirements of the design

- 4) Determine resource layout of the target device

PACE is used during initial design entry or after consolidation of a design into a netlist file. For initial design entry, PACE reads and writes VHDL and Verilog files limited to I/O definitions. For consolidated netlists, PACE reads the NGD file. In both cases, PACE reads and writes user constraint files (UCFs).

To learn more about PACE and how to use it in Active-HDL, go to Active-HDL Online Documentation, then in the Contents tab select Active-HDL Help / Active-HDL Tools /Design Flow Manager /Multivendor Flowchart/ Launching Additional Flow Tools/Xilinx/PACE Options Dialog Box.

Constraints Editor is a program that you can use to create and modify the most commonly used constraints

To learn more about Constraints Editor and how to use it in Active-HDL, go to Active-HDL On-line Documentation, then in the Contents tab select Active-HDL Help / Active-HDL Tools /Design Flow Manager /Multivendor Flowchart/ Launching Additional Flow Tools/Xilinx/Constraints Editor Options Dialog Box.

Using PACE and Constraints Editor, you can prepare a customized Xilinx constraints file (ucf) file.

A simple example of Xilinx constraints file for design freq\_meter targeted to virtex family v50cs144 device looks like in Figure 29. Please note that this is a very basic Xilinx constraints file with Pin names and locations on the device. Please refer to Xilinx Documentation and Xilinx PACE and Constraints Editors (which can be launced from Active-HDL) on how to write constraints files for FPGA design targeted to Xilinx FPGAs.

| NET | F_INPUT       | LOC=A6;  |

|-----|---------------|----------|

| NET | F_PATTERN     | LOC=A7;  |

| NET | RESET LOC     | C=G1;    |

| NET | START LOC     | C=H1;    |

| NET | LED_A<2>      | LOC=A8;  |

| NET | LED_C<4>      | LOC=B7;  |

| NET | LED_C<1>      | LOC=B10; |

| NET | LED_C<3>      | LOC=C8;  |

| NET | LED_C<5>      | LOC=C9;  |

| NET | LED_C <o></o> | LOC=C13; |

| NET | LED_A<3>      | LOC=D8;  |

| NET | LED_C<2>      | LOC=D12; |

| NET | LED_C<6>      | LOC=E13; |

| NET | LED_A<5>      | LOC=F12; |

| NET | LED_A<1>      | LOC=F13; |

| NET | LED_A<6>      | LOC=G13; |

| NET | LED_A <o></o> | LOC=H13; |

| NET | $LED_A < 4 >$ | LOC=K11; |

| NET | LED_B <o></o> | LOC=K13; |

| NET | LED_B<5>      | LOC=L11; |

| NET | LED_B<3>      | LOC=M11; |

| NET | LED_B<4>      | LOC=N11; |

| NET | LED_B<6>      | LOC=N8;  |

| NET | LED_B<1>      | LOC=N9;  |

| NET | LED_B<2>      | LOC=M8;  |

| NET | LED_D <o></o> | LOC=M10; |

| NET | LED_D<4>      | LOC=K9;  |

| NET | LED_D<3>      | LOC=K8;  |

| NET | LED_D<6>      | LOC=K4;  |

| NET | LED_D<5>      | LOC=K5;  |

| NET | LED_D<1>      | LOC=K6;  |

| NET | LED_D<2>      | LOC=N5;  |

|     |               |          |

# Figure 29: Simple Example of Xilinx I/O Constraints file (Xilinx.ucf)

# Please click here to download the Xilinx.ucf file

# Implementation with Xilinx ISE and Providing Implementation Constraints

To run the Xilinx Implementation, similar steps are taken as for synthesis.

|    |                                            | options |                |

|----|--------------------------------------------|---------|----------------|

| 1. | Click on the implementation options button | [       | implementation |

] in the Design Flow Manager.

- 2. Select the simulation output format as *VHDL* and running mode as *Batch*.

- 3. You can set other implementation options also in this area.

| Implementation (   | Options                                                             |                       |

|--------------------|---------------------------------------------------------------------|-----------------------|

| Main Core Inse     | ertion \/ Translate \/ Map \/ Advanced Map \/ Post-Map STR \/ Place | & Route VPost-PAR STR |

| Netlist File       | c:/My_Designs/Samples_73/Freq_meter/synthesis/freq_top.ngc          | Browse                |

| Family             | Xilinx9x VIRTEX VIRTEX V50cs144                                     | ✓                     |

| Speed Grade        | -6                                                                  |                       |

|                    | Version : ver1 Revision : rev1                                      |                       |

| Simulation Outpu   | ut Format C None 📀 VHDL C Verilog                                   |                       |

| Run Mode: 🤅        | Batch C GUI                                                         | T Auto-close          |

| Generate Synth.    | . and Impl. Script                                                  | Generate Impl. Script |

| 🔽 Overwrite e      | xisting impl. proj.                                                 |                       |

| 🔲 Filter Messa     | iges                                                                | Browse                |

|                    |                                                                     |                       |

| Constraint File (L | JCF) Support: Custom constraint file                                |                       |

|                    | t file to be copied into the implementation folder:                 | Browse                |

|                    | Samples_73/Freq_meter/constraints/xilinx.ucf                        |                       |

|                    | entation with selected command file (implement.bat):                | Browse                |

| IJ                 |                                                                     |                       |

|                    |                                                                     |                       |

|                    |                                                                     |                       |

|                    |                                                                     |                       |

|                    | ОК                                                                  | Cancel Help           |

|                    |                                                                     |                       |

Figure 30: Xilinx ISE\WebPack Implementation Options with Xilinx.ucf selected as Custom constraints File

#### In the Constraint File (UCF) Support field, there are three options to specify implementation constraints.

| Constraint File (UCF) Support:         | Always synchronize with the synthesis generated constraint file                           |   |

|----------------------------------------|-------------------------------------------------------------------------------------------|---|

| Select constraint file to be copied in | Always use Aldec constraint template                                                      | ~ |

| Cultur DecignelSamples 72/Erea -       | Always synchronize with the synthesis generated constraint file                           |   |

| Jc:/my_besigns/bampies_/b/rred_i       | Always synchronize with the synthesis generated constraint file<br>Custom constraint file |   |

Figure 31: Select Constraints File Options

#### Always use Aldec constraint template

Specifies to fetch during implementation the constraint template delivered with Active-HDL (\$ALDEC\Dat\Template.ucf). The path to the template is displayed in the Select constraint file to be copied into the implementation folder edit box. When this option is selected, the Browse button is disabled. Note that \$ALDEC\Dat\Template.ucf file is just a template. You have to modify this to include the constraints for the design.

#### Always synchronize with the synthesis generated constraint file

Specifies to fetch during implementation the constraint file generated by the selected synthesis tool. This option is selected automatically when Synplify/Synplify Pro and Xilinx tools are in use. The path to the file is displayed in the Select constraint file to be copied into the implementation folder edit box. When this option is selected, the Browse button is disabled.

#### **Custom constraint file**

6.

Specifies to fetch during implementation a user-defined constraint file.(example is Xilinx.ucf as discussed above) When this option is selected, the Browse button is enabled and you can point to the constraint file that you have downloaded in the dialog box. The path to the file is displayed in the Select constraint file to be copied into the implementation folder edit box.

- implementation 4. When you are done with the settings, click **OK**. Click **Implementation** tab [ on the design flow manager.

- 5. While the Implementation is running, all of the Implementation results and information can be seen on-line in a special window.

| Xilinx Implemente                                   | ation            |                            |        |

|-----------------------------------------------------|------------------|----------------------------|--------|

| Translate                                           | Map<br>Completed | ➡ Post-Map ST<br>Completed | ➡<br>R |

| umber of warni:<br>umber of info<br>otal memory us: | messages: 1      | lohutes                    |        |

| 74 Xilinx Implementa                                                                                                                    | tion            |                      |             |              |           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|-------------|--------------|-----------|--|

|                                                                                                                                         |                 | →                    |             | →            |           |  |

| Translate                                                                                                                               | Мар             | Post-Map STR         | Place&Route | Post-PAR STR | Timing    |  |

| Completed                                                                                                                               | Completed       | Completed            | Completed   | Completed    | Completed |  |

| Number of warnings: 0<br>Number of info messages: 1<br>Total memory usage is 71748 kilobytes<br>Created netgen log file 'time sim.nlf'. |                 |                      |             |              |           |  |

| -                                                                                                                                       | ver1->rev1: 0 e | rror(s), O warning(s | )           |              | -         |  |

| 1                                                                                                                                       |                 |                      | Close       |              |           |  |

Figure 32: Xilinx ISE/WebPack implementation window in batch mode.

30

......

7. Implementation reports can then be viewed by clicking on the corresponding implementation **reports** button in the Design Flow Manager.

| Implementation Reports                  | X     |

|-----------------------------------------|-------|

|                                         |       |

| Place & Route                           |       |

| Pad                                     |       |

| Post-Place & Route Static Timing Report |       |

| Post-Map Static Timing Report           |       |

| ×                                       |       |

|                                         |       |

| Implement Log                           | -     |

| 4                                       |       |

| Open Report                             | Close |

Figure 33: Implementation Reports Window.

If Implementation is run in **batch mode**. All files will be automatically passed to the Implementation tool and when task is complete; all results will be passed to Active-HDL. If you run in **GUI mode**, then Active-HDL passes all the necessary design files to the Implementation tool.

After Successful Implementation of the design, Implementation tool generates implementation report constraints file, *freq\_top\_pad.csv* in the *C:\My\_Designs\Samples\_73\Freq\_meter\implement\ver1\rev1* folder.

#### Implementation with Xilinx ISE/WebPack in GUI Mode

1. To run the implementation in GUI mode select *run mode* to GUI in implementation options.

#### Figure 34: Selecting Run mode for the implementation

- 2. You can select and set other Implementation options also from the window.

- 3. When you are done with all the settings you can click on OK.

- 4. Now you can automatically perform push-button Implementation by clicking the *Implementation*

[implementation] button in the Design Flow Manager.

5. You will see the Xilinx ISE Project Navigator running on the screen. When you see the process is over you can go back to Active-HDL and click on the *refresh file list* tab.

Figure 35: Refreshing implementation file lists

6. You will be prompted with choose source files window. Make sure you select the correct file if they have not been selected automatically by tool. Hit **OK** now.

| Choose source files |                                                            |        |  |  |

|---------------------|------------------------------------------------------------|--------|--|--|

| Timing netlist :    | c:/My_Designs/Samples_73/Freq_meter/implement/time_sim.vhd |        |  |  |

| SDF file :          | c:/My_Designs/Samples_73/Freq_meter/implement/time_sim.sdf |        |  |  |

|                     | ОК                                                         | Cancel |  |  |

Figure 36: Choosing source files

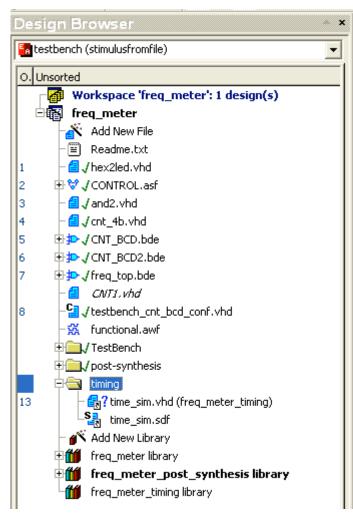

7. You will see new folder *timing* and new library freq\_meter\_timing library created in design browser.

Figure 37: Design browser after Implementation

# **Timing Simulation**

Timing simulation uses the output files created by the implementation tool. Depending on the current implementation options, the implementation tool generates VHDL code, Verilog code, or EDIF netlist.

1. Click on the options [ options

iming simulation tab.

2. Here you should be able to see .sdf in the *SDF File* box and *Input files* box contains output vhdl netlist file of the implementation.

| Timing Simulation Options |                               |  |  |  |  |

|---------------------------|-------------------------------|--|--|--|--|

| General Server Farm       |                               |  |  |  |  |

| Run With Selected Options |                               |  |  |  |  |

|                           |                               |  |  |  |  |

| SDF File                  | implement/time_sim.sdf        |  |  |  |  |

| SDF Type                  | C Minimum 📀 Typical C Maximum |  |  |  |  |

| Input Files:              | 🛅 🔀 🗲                         |  |  |  |  |

| implement/time_sim.vhd    |                               |  |  |  |  |

Figure 38: Timing simulation files in Options tab

3. Click on icon to add your timing netlist. Select the proper files from the list appeared in the new window and click on the *arrow tab* to add them to the list and then click *Ok* to back to options window. Add the TestbenchPack.vhd and testbench.vhd in that order.

| Select design files                                                                                                                                                                                                                             |                                                                                                      |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

| <pre>src/hex2led.vhd src/CONTROL.asf src/and2.vhd src/cnt_4b.vhd src/CNT_BCD.bde src/CNT_BCD2.bde src/Ireq_top.bde src/CNT1.vhd src/TestBench/TestBenchPack.vhd src/TestBench/testbench.vhd synthesis/freq_top.vhd IMPLEMENT/TIME_SIM.VHD</pre> | N     IMPLEMENT/TIME_SIM.VHD       src/TestBench/TestBenchPack.vhd       src/TestBench/testbench.vhd |  |  |  |  |

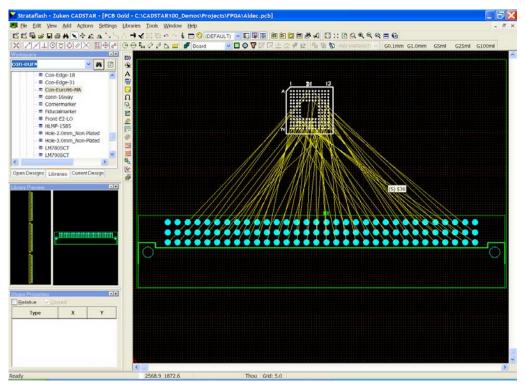

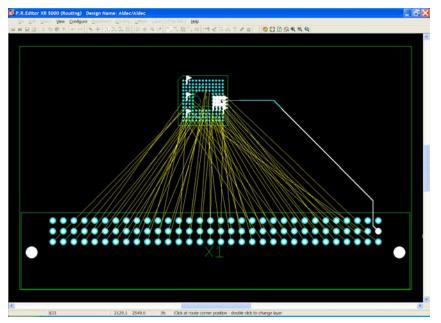

Figure 39: Adding timing netlist and testbench files for simulation